SSD_Frequency Adjustment

1. Overview¶

The ssd2xx series chips support dynamic adjustment of the Core Power voltage.

Core Power voltage is determined by two factors: CPU frequency and chip temperature, and other chips may be determined by other factors.

The kernel-related define is CONFIG_SS_VOLTAGE_CTRL.

2. CPU frequency and Core Power¶

CPU frequency=800MHz, Core Power 0.9V

CPU frequency=1GHz, Core Power 1.0V

No matter how much the CPU frequency software is set, it needs Core Power = 1V to start.

Recommended practice: The hardware retains the DVFS circuit, 1V starts, and the voltage is selected according to the main frequency configured by the software after starting.

If the hardware requires fixed Core Power, please confirm the risk with SigmaStar first.

2.1. Software fixed frequency 1G¶

Notice:

-

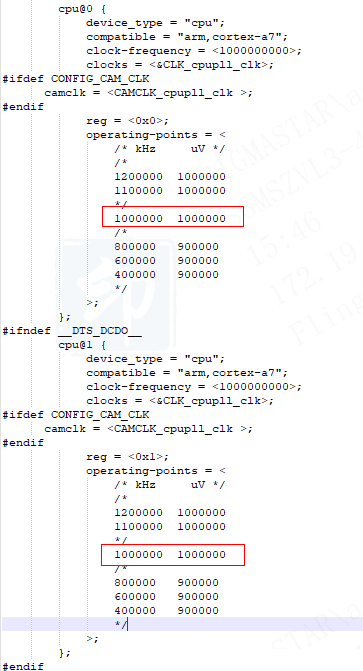

Fixed cpu frequency in

kernel\arch\arm\boot\ dts \pioneer3.dtsi, such as fixed to 1Ghz

-

After kernel config opens CONFIG_SS_VOLTAGE_CTRL, the software under Kernel will control the core pin

-

The software will not control DVFS in the IPL/UBOOT stage. When KERNEL is up, the software will set Core Power=1.0V

-

The pin of the hardware to dynamically adjust the core voltage has been connected to the relevant circuit

-

Actual measurement to see if it meets the following settings: from power-on to IPL/UBOOT/KERNEL has been maintained at 1.0V

2.2. Fixed frequency 800M¶

Notice:

-

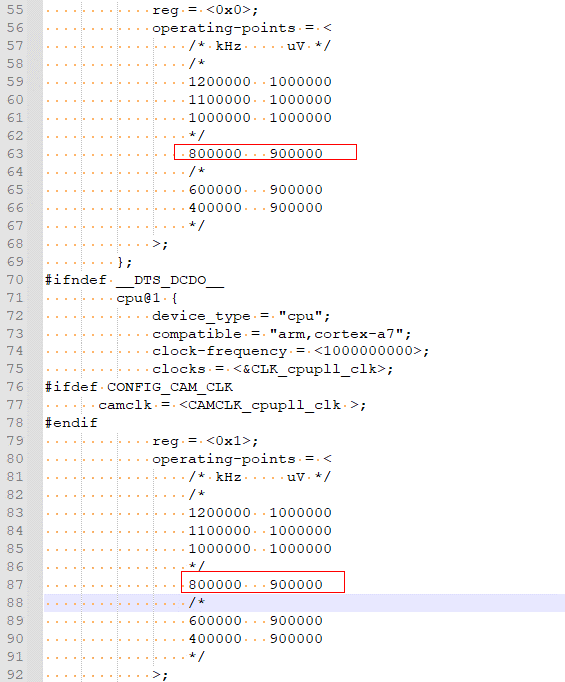

Fixed cpu frequency in

kernel\arch\arm\boot\ dts \pioneer3.dtsi, such as fixed to 800M

-

After kernel config opens CONFIG_SS_VOLTAGE_CTRL, the software under Kernel will control the core pin

-

The software will not control DVFS in the IPL/UBOOT stage. When KERNEL is up, the software will set Core Power=0.9V

-

The pin of the hardware to dynamically adjust the core voltage has been connected to the relevant circuit

-

Actual measurement to see if it meets the following settings: from power-on to IPL/UBOOT has been maintained at 1.0V, KERNEL is switched to 0.9V (CPU 800MHz)

2.3. Dynamic frequency 1G/800M¶

Dynamic adjustment according to needs, need to pay attention to:

-

Fixed cpu frequency in

kernel\arch\arm\boot\ dts \pioneer3.dtsi, such as fixed to 800M

-

After kernel config opens CONFIG_SS_VOLTAGE_CTRL, the software under Kernel will control the core pin

-

The software will not control DVFS in the IPL/UBOOT stage. When KERNEL is up, the software will set Core Power=0.9V

-

The pin of the hardware to dynamically adjust the core voltage has been connected to the relevant circuit

-

Actual measurement to see if it meets the following settings: from power-on to IPL/UBOOT has been maintained at 1.0V. After KERNEL is up, switch Core Power according to the main frequency selected by the software, CPU 800MHz → 0.9V or CPU 1G → 1.0V

Check the current cpu frequency: cat /sys/devices/system/cpu/cpufreq/policy0/cpuinfo_cur_freq

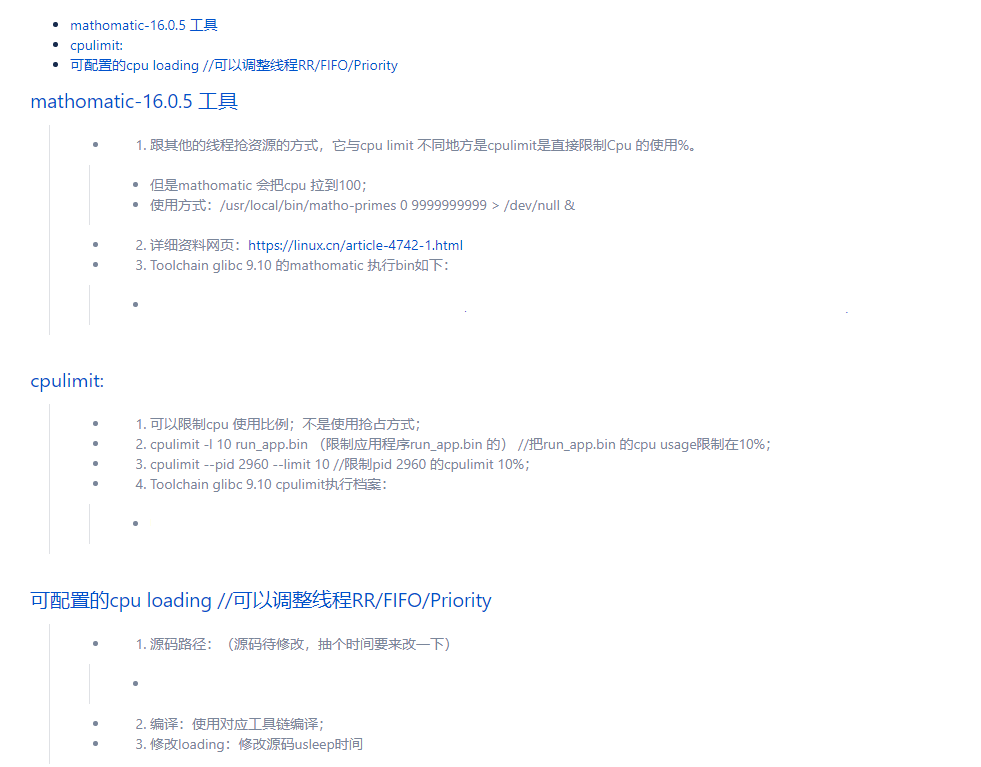

Pull up cpu loading:

The following attachments are compiled and can be used directly:

3. Tsensor temperature and core power¶

Below 40 degrees: Require Core Power 1V

40 degrees to 60 degrees: Maintain the last core power, no change

Above 60 degrees: Require Core Power 0.9V

View current cpu temperature: cat /sys/devices/virtual/mstar/msys/TEMP_R

4. Common debug methods and commands¶

The actual effect of core power is determined by " cpu temperature" and "cpu loading", which can be view by

cat /sys/devices/system/voltage/core/voltage_current.

As long as one of the two needs 1v, it will always pull the core power to 1V.

The following debug commands are commonly used:

cat /sys/devices/system/voltage/core/ voltage_current

→View the current core power voltage

cat /sys/devices/system/voltage/core/ voltage_available

→View the core power voltage gear and the corresponding gpio

cat /sys/devices/virtual/ mstar / msys /TEMP_R

→View current cpu temperature

cat /sys/devices/system/ cpu / cpufreq /policy0/ cpuinfo_cur_freq

→View current cpu frequency

cat /sys/devices/system/ cpu / cpufreq /policy0/ cpuinfo_max_freq

→View max cpu frequency

cat /sys/devices/system/ cpu / cpufreq /policy0/ cpuinfo_min_freq

→View min cpu frequency