Panel配置参考

1. 基本介绍¶

1.1. 概述¶

本文档主要讲解点屏相关的配置和使用。

1.2. 关键字说明¶

-

TTL/MIPI/SRGB

TTL 接口信号类型是TTL电平,信号的内容是RGB565或RGB666或RGB888,行场同步(HSYNC/VSYNC),时钟(CLK)和数据有效信号(DE)。

MIPI 接口信号类型是LVDS信号,信号的内容是视频流数据和控制指令。

SRGB 接口将一个像素点的RGB数据被分为三次传输到panel。

-

HDMI

高清多媒体接口(High Definition Multimedia Interface)是一种全数字化视频和声音发送接口,可以发送未压缩的音频及视频信号。

2. TTL点屏介绍¶

2.1. 基本概念¶

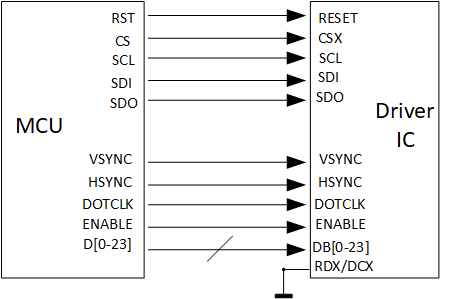

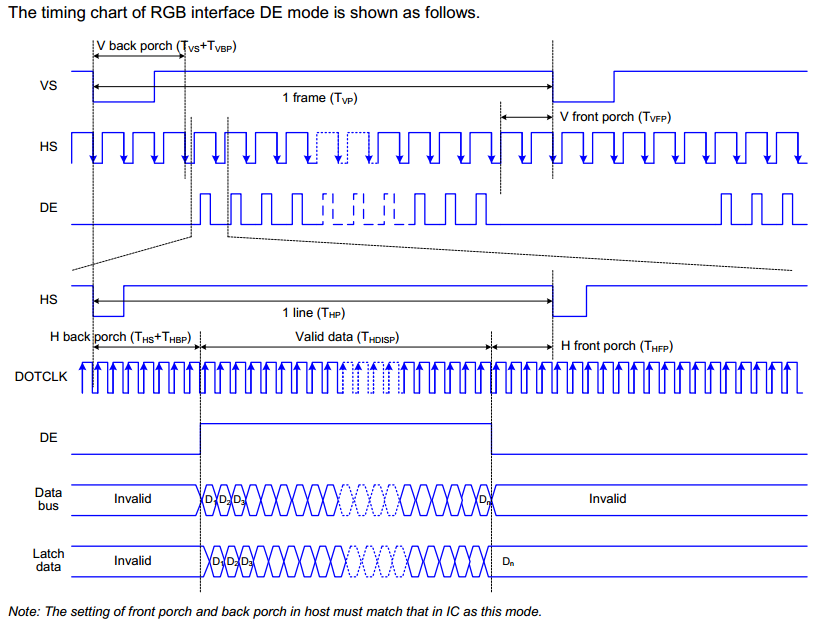

Parallel RGB Interface有两种,DE mode和HV mode,当使能DE的时候,会使用VSYNC、HSYNC、DOTCLK、DE、D[0-23]这些pin,当使能HV mode的时候,会使用VSYNC、HSYNC、DOTCLK、D[0-23]。现在程序默认使用DE mode,相关参数请按照DE mode配置。

一些panel driver IC需要对其初始化,其实就是对其内部register的设定,一般会通过SPI或者IIC接口来通信,初始化需要的cmd和data一般由屏厂提供,发送时的数据格式需要参考panel datasheet。

使用Parallel RGB Interface的panel需要HSYNC、VSYNC、DOTCLK来作为同步信号,RGB data只在timing的特定区间有效。

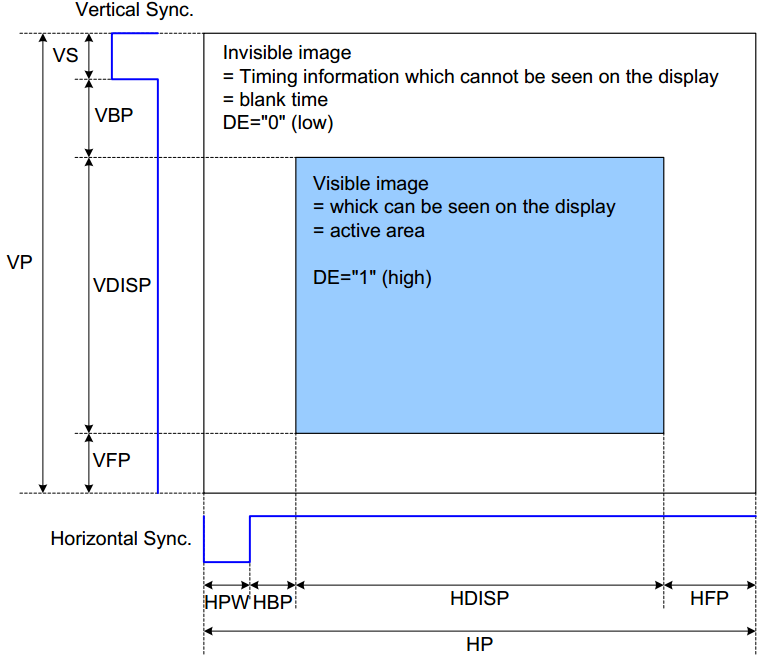

行场信号中的blanking区间是不可见区域,只有active区间的RGB data才会最终显示出来,不同的panel Driver IC对于blanking区间的要求不同。

行信号中:

Htotal = HSYNC + HBP + HFP + H Active

场信号中:

Vtotal = VSYNC + VBP + VFP + V Active

最后计算像素时钟频率:

Pixel CLK = Htotal * Vtotal * fps

屏参中时序相关的配置主要是调整行信号中HSYNC、HBP、HFP和场信号中VSYNC、VBP、VFP。panel spec中会提供blanking区间各部分的长度要求。

blanking区间是一个可调范围,最终计算出的pixel clk也是在一个范围内。

主控芯片一般会有时钟频率的限制,所以在点一个新的panel时,应先计算panel的pixel clk,如果将要点的panel满足像素时钟频率的要求,则一般可以点起来。

Parallel RGB Interface Timing:

2.2. 点屏流程¶

2.2.1. 硬件相关¶

2.2.1.1. 查看原理图

我们用SSU 9383 demo board原理图举例说明。

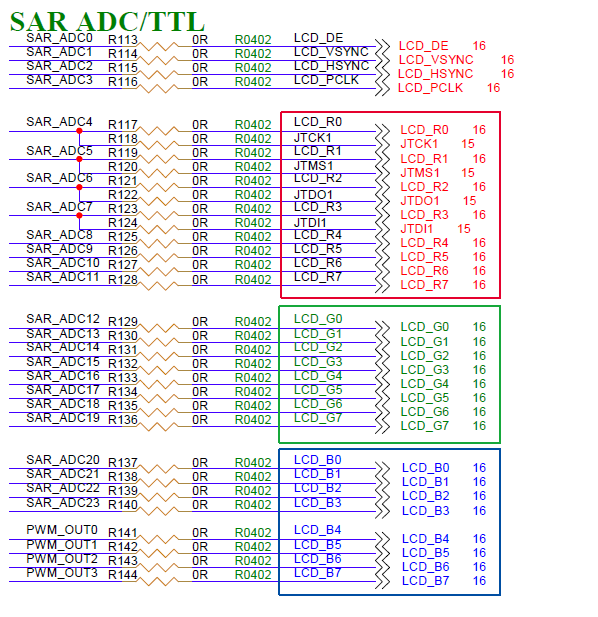

查看如下原理图知道RGB888数据格式,知道CLK/HSYNC/VSYNC/DE对应的Pin:

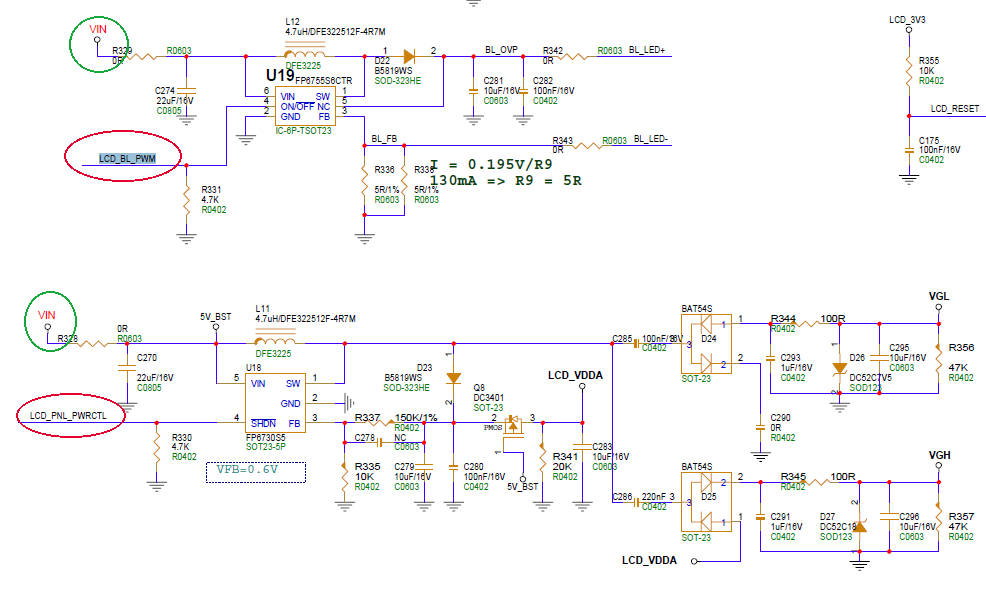

查看如下原理图知道控制时序需要的PWM(LCD_BL_PWM)和panel power enable(PNL_PWRCTL):

-

对应芯片端如下pin:

2.2.1.2. 对应的Padmux

查看SSU 9383 HW CheckList V1.0.xlsx的Tmux页找到管脚对应的padmux,如下:

-

信号管脚

-

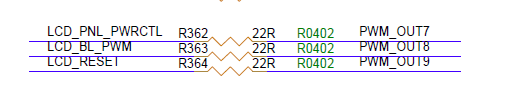

控制管脚

2.2.2. 软件相关¶

2.2.2.1. 配置padmux

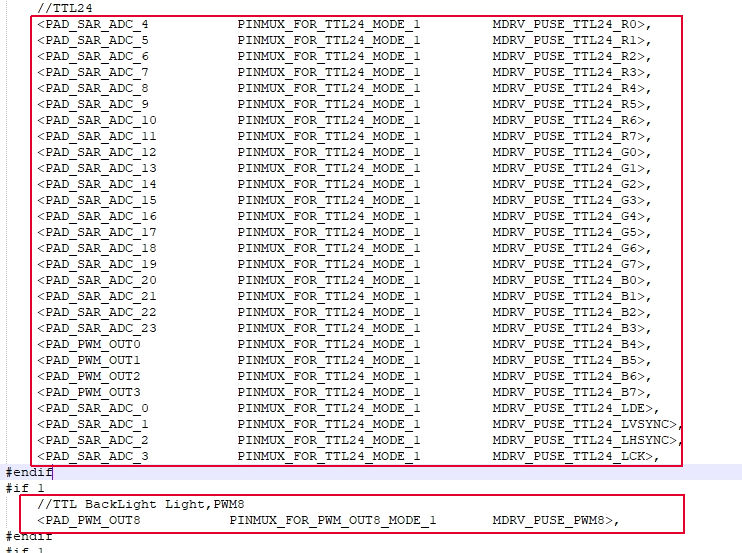

通过如上知道panel使用的是ttl24_mode_1,对应kernel的pioneer5-ssc028a-s01a_demo-padmux.dtsi(使用的config不一样话对应的padmux.dtsi不一样)配置如下:

2.2.2.2. 配置控制管脚(pwm/power)

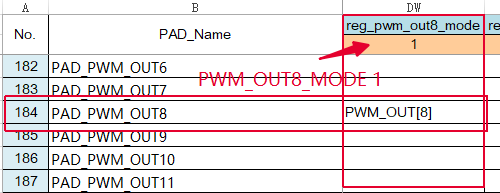

通过原理图我们知道panel 背光使用的是pwm_out8_mode1

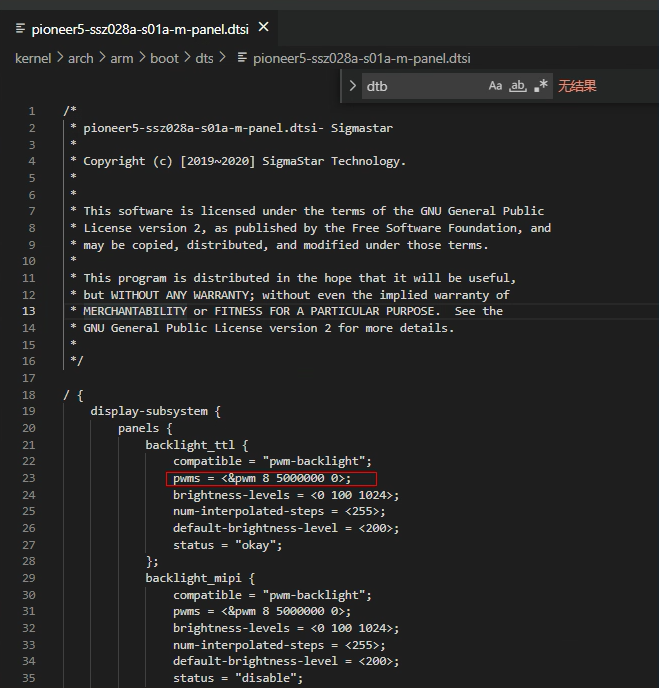

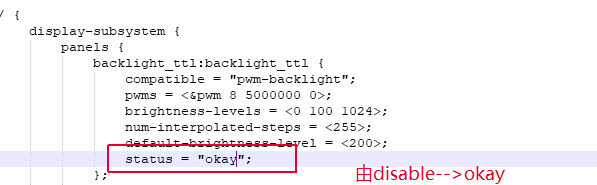

kernel的pioneer5-ssz028a-s01a-m-panel.dtsi(使用的config不一样话对应的backlight.dtsi不一样) 配置如下:

-

使能对应配置:

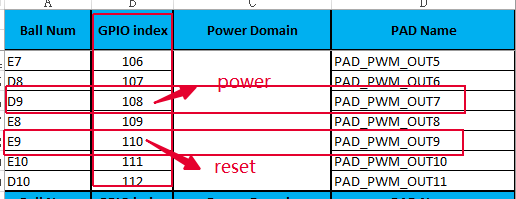

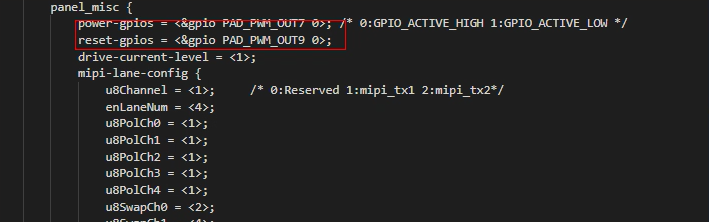

通过原理图我们知道power 和 reset 对应的gpio是PAD_PWM_OUT7,PAD_PWM_OUT9 查看SSU 9383 HW CheckList V1.0.xlsx的IO Mapping页

kernel的pioneer5-ssz028a-s01a-m-panel.dtsi(使用的config不一样话对应的panel-misc.dtsi不一样) 配置如下:

2.2.2.3. 屏参配置

-

新增屏参

-

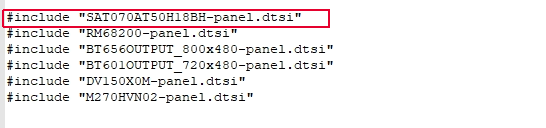

SSU 9383 采用dtsi的形式配置屏参,先找一个公版Demo带的屏参文件,这里拿公版TTL的屏参SAT070AT50H18BH-panel.dtsi举例(该头文件易见于公版各显示Demo)

-

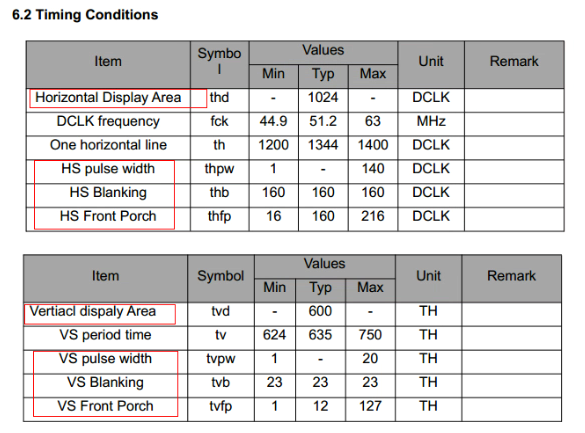

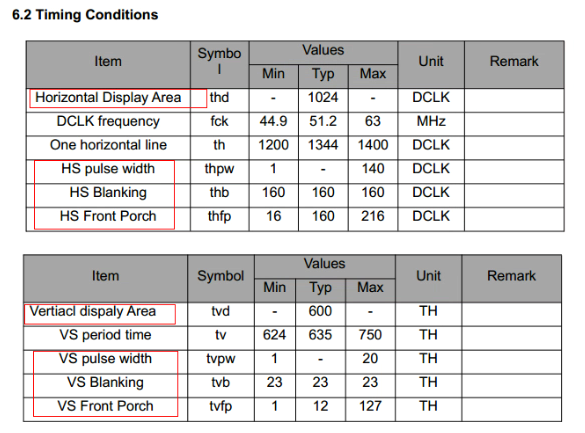

确认屏规格书,找到对应Timing规格,如:

HTotal = u16Width + u16HSyncWidth + u16HSyncBackPorch + HSyncFrontPorch VTotal = u16Heigth + u16VSyncWidth + u16VSyncBackPorch + HVyncFrontPorch DCLK = HTotal * VTotal * FPS

-

参考以下屏参参数说明,将屏规格对应的参数填写到panel.dtsi中

参数 描述 name panel name interface 接口类型:TTL/MIPI/LVDS/BT1120/BT656 clock-frequency clock 频率 hactive 行有效像素点数 hfront-porch 行同步信号前肩 hback-porch 行同步信号后肩 hsync-len 行同步信号脉宽 hsync-actice 行同步信号极性 vactive 场有效行数 vfront-porch 场同步信号前肩 vback-porch 场同步信号后肩 vsync-len 场同步信号脉宽 vsync-actice 场同步信号极性 de-active de信号极性 pixelclk-active pclk极性 output-bit-mode 10BIT :0; 6BIT :1; 8BIT :2; 565BIT :3 panel-swap-R Swap Channel R: 0:default; 1:select R; 2:select G; 3:select B panel-swap-G Swap Channel G: 0:default; 1:select R; 2:select G; 3:select B panel-swap-B Swap Channel B: 0:default; 1:select R; 2:select G; 3:select B panel-swap-ML Swap Rgb MSB/LSB 0:disable M/L swap; 1:enable M/L swap

-

-

示例

SAT070AT50H18BH-panel.dtsi

/ { display-subsystem { panels { SAT070AT50H18BH { compatible = "sstar,panel"; name = "SAT070AT50H18BH"; interface = "TTL"; /* TTL/MIPI/LVDS/BT1120/BT656 */ misc = <&panel_misc>; backlight = <&backlight_ttl>; status = "okay"; port { SAT070AT50H18BH_in_dpi: endpoint { remote-endpoint = <&dpi_out_panel>; }; }; panel-timing { clock-frequency = <51000000>; hactive = <1024>; hfront-porch = <222>; hback-porch = <46>; hsync-len = <52>; hsync-active = <0>; vactive = <600>; vfront-porch = <8>; vback-porch = <23>; vsync-len = <4>; vsync-active = <0>; de-active = <0>; pixelclk-active = <0>; }; }; }; }; };

2.2.2.4. 配置加载对应屏参

kernel的pioneer5_display-subsystem.dtsi 配置如下:

-

先include 对应的屏参配置文件

-

选择对应屏参文件,并使能

3. MIPI点屏介绍¶

3.1. 规格¶

MIPI DSI 规格:

- 1-4 data lanes, 1 clock lane

- Level:

- LP: 0~12V

- HS: 100~300mV

- HS: 80Mbps ~ 1.5Gbps/lane

- Pixel format:

- 16 bpp (5,6,5 RGB) each pixel using two bytes

- 18 bpp (6,6,6 RGB) packed

- 18 bpp (6, 6, 6 RGB) loosely packed into three bytes

- 24 bpp (8, 8, 8 RGB), each pixel using three bytes

- video mode: BURST_MODE/SYNC_EVENT/SYNC_PULSE

- data/clk chn swap

- data/clk chn P/N swap

- data clk skew adjustment

3.2. 基本概念¶

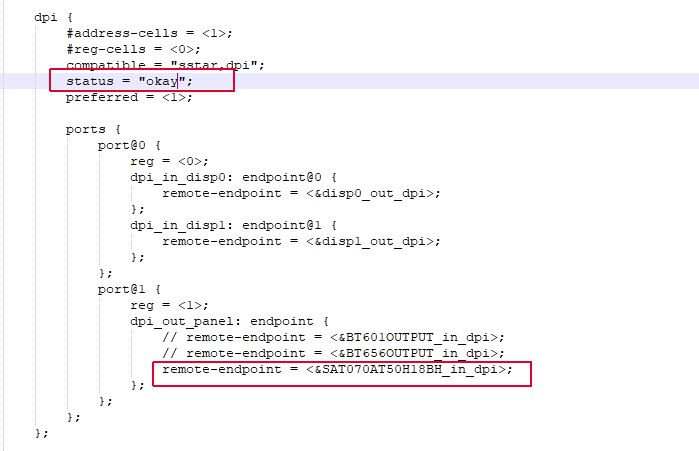

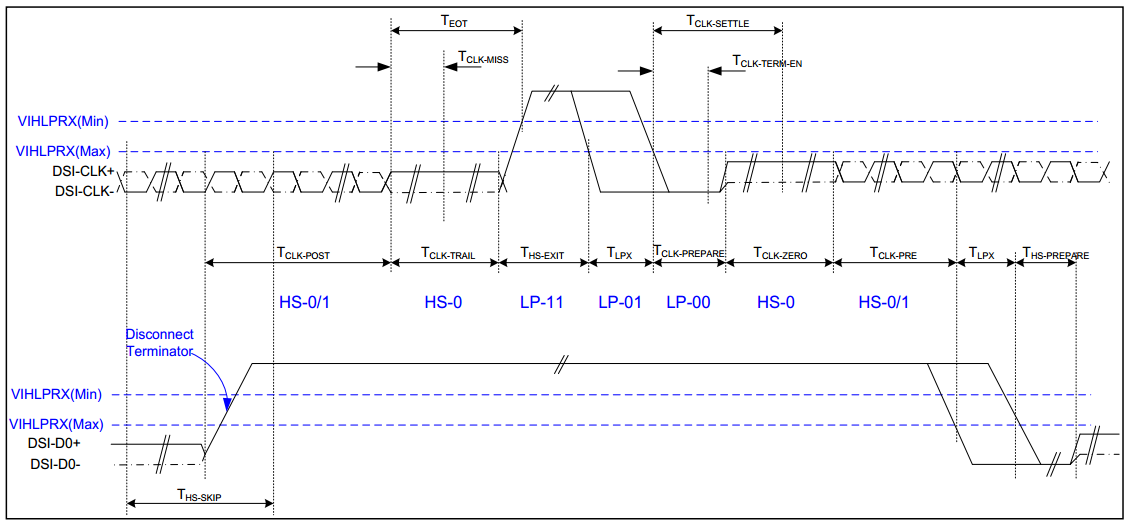

3.2.1. MIPI DPHY timing chart¶

3.2.2. Configure HS Timing Parameter¶

HS_TRAIL / HS_EXIT / HS_PRPR / HS_ZERO / CLK_PRPR / CLK_ZERO / CLK_POST / CLK_TRAIL

| Timing specification | |

|---|---|

| T_{HS-PREPARE} + T_{HS-zero} | 145ns+10*UI |

| T_{HS-PREPARE} | 40ns+4*UI ~ 85ns+6*UI |

| T_{HS-zero} | > 60ns+4*UI ~ 105n+6*UI |

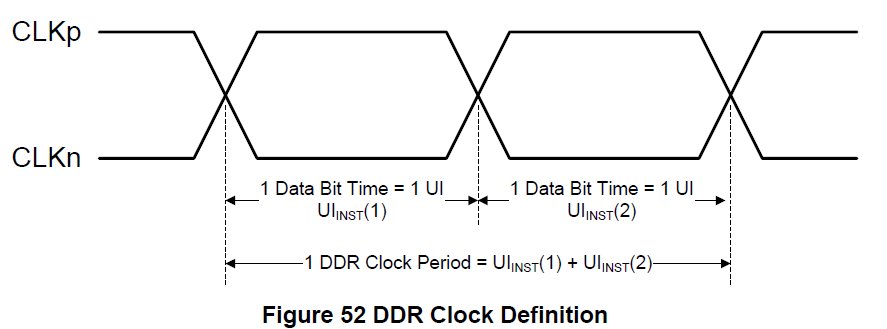

UI表示时间间隔,等于时钟通道上任何HS状态的持续时间.

UI的计算方法:

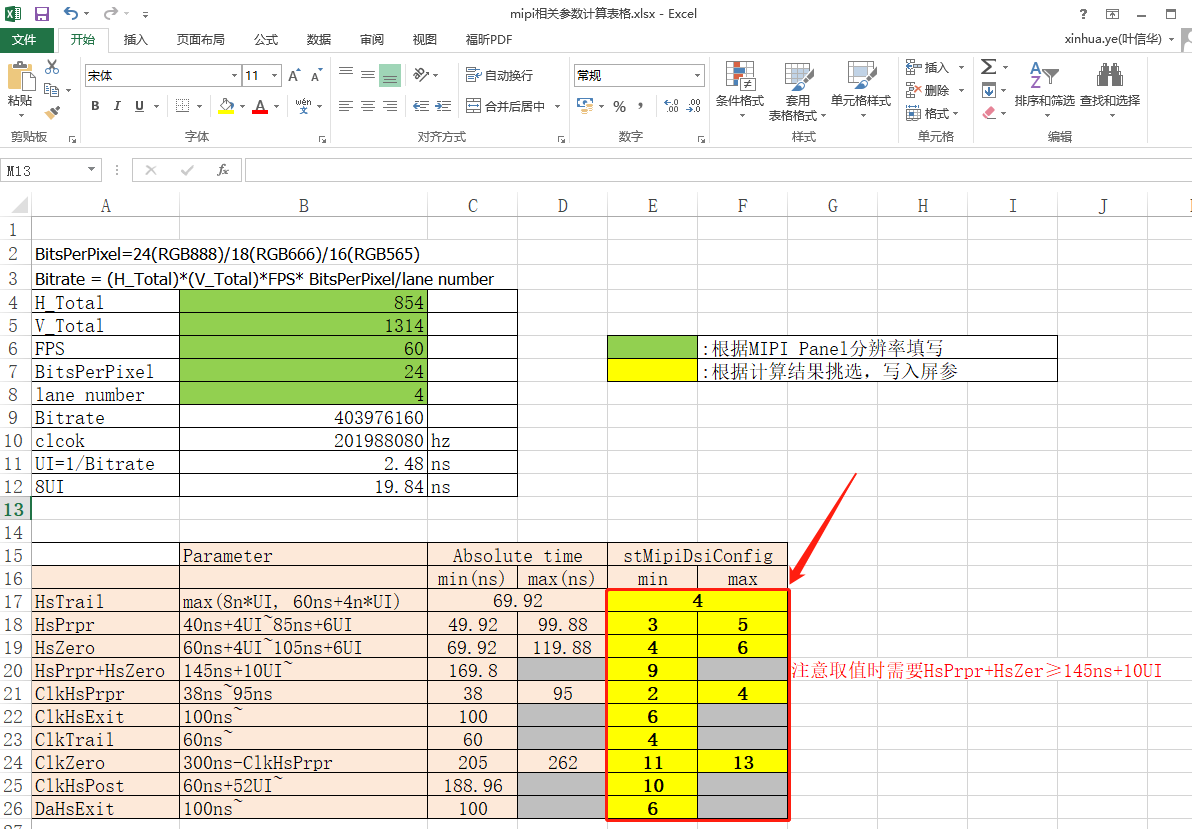

H_Total = HACT+HPW+HBP+HFP V_Total = VACT+VPW+VBP+VFP BitsPerPixel=24(RGB888)/18(RGB666)/16(RGB565) Bitrate = (H_Total)*(V_Total)*FPS* BitsPerPixel/lane number UI = 1/Bitrate

如果Bitrate = 750Mps,UI = 1/Bitrate = 1.333ns,那么HS timing parameter计算结果为:

| Timing specification | Absolute time | DA_HS_PREP value(Absolute time/(8*UI)) | |

|---|---|---|---|

| T_{HS-PREPARE} + T_{HS-zero} | 145ns+10*UI | > 158.33 ns | > 15 |

| T_{HS-PREPARE} | 40ns+4*UI ~ 85ns+6*UI | 45.32 ~ 92.98 ns | 5-8 |

| T_{HS-zero} | >60ns+4*UI ~ 105ns+6*UI | > 112.98 ~ 65.32 ns | 10-7 |

3.2.3. Configure LP Timing Parameter¶

CONT_DET/LPX/TA_GET/TA_SURE/TA_GO

low power parameters建议使用提供的默认值

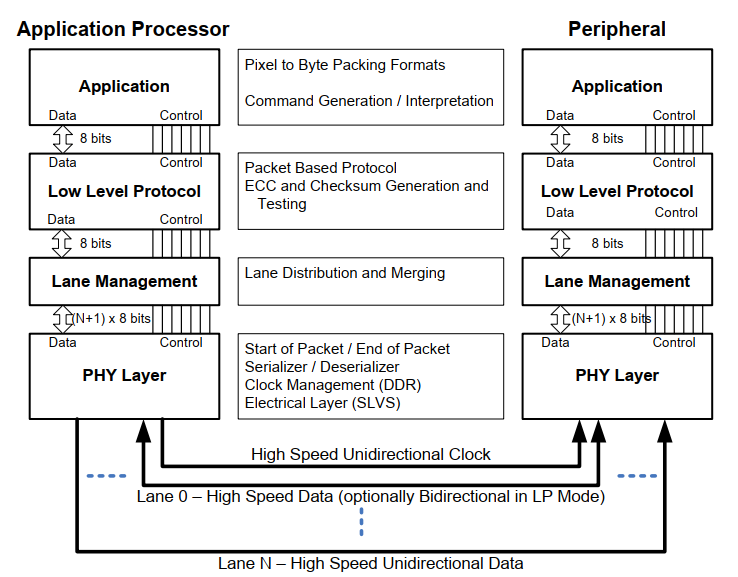

DCS(Display Command Set)协议

DCS是一个标准化的命令集,用于命令模式的显示模组。

DSI(Display Serial Interface)分四层,对应D-PHY、DSI、DCS规范、分层结构图如上:

- PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

- Lane Management层:发送和收集数据流到每条lane。

- Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

- Application层:描述高层编码和解析数据流。

3.3. 点屏流程¶

3.3.1. 硬件相关¶

3.3.1.1. 查看原理图

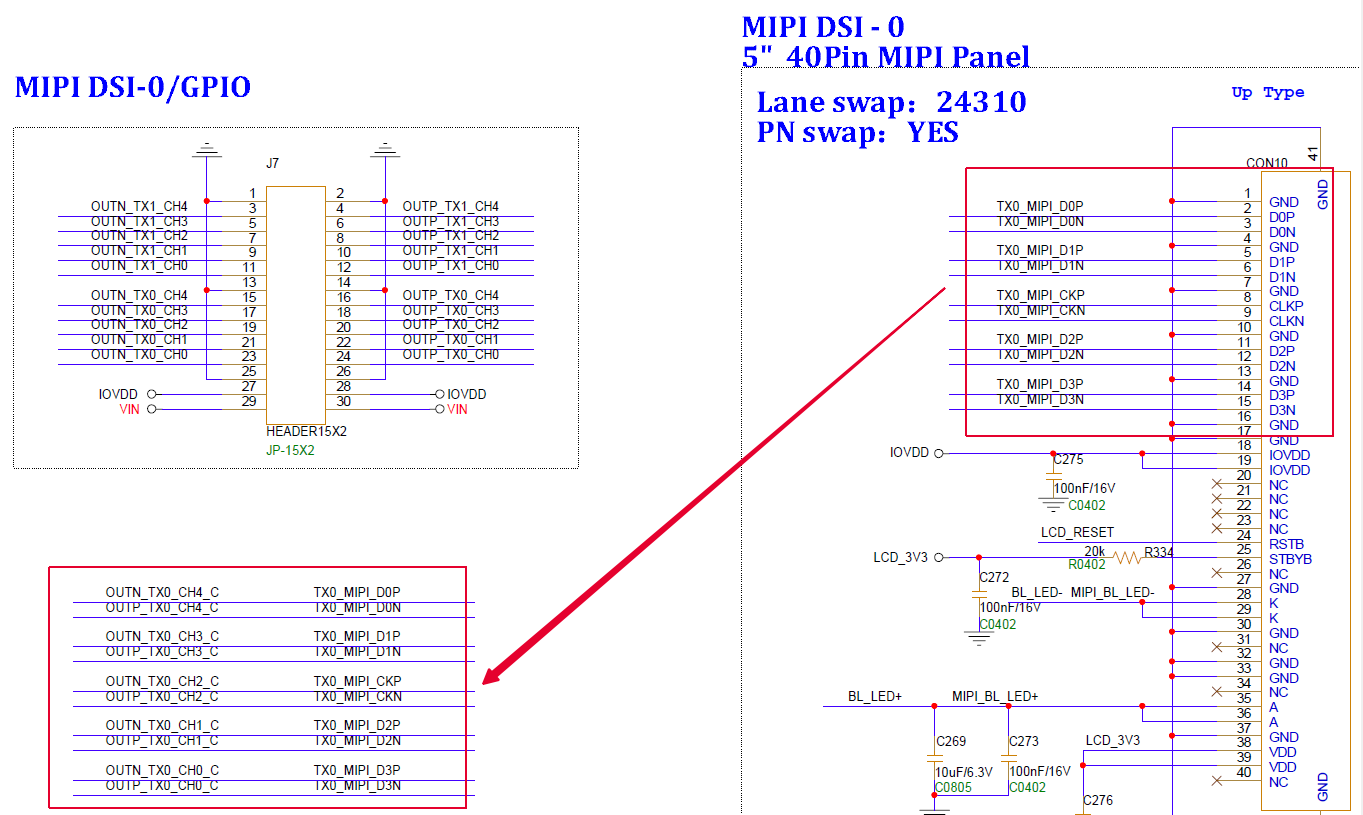

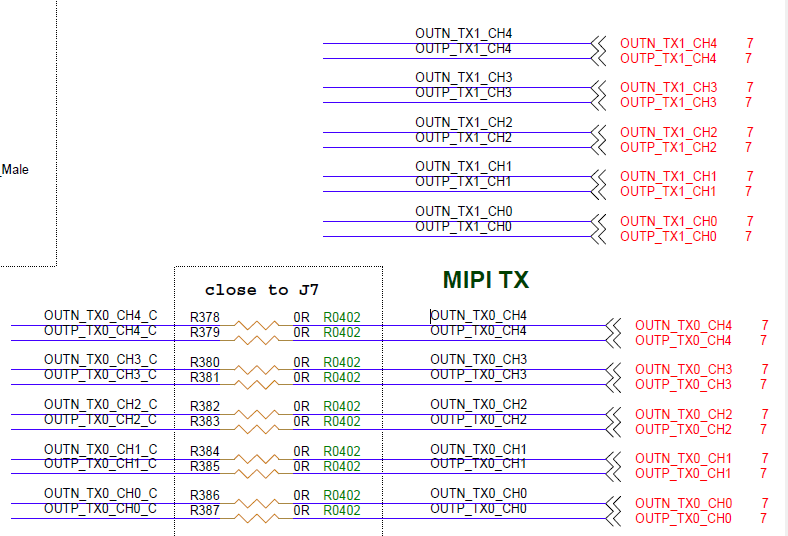

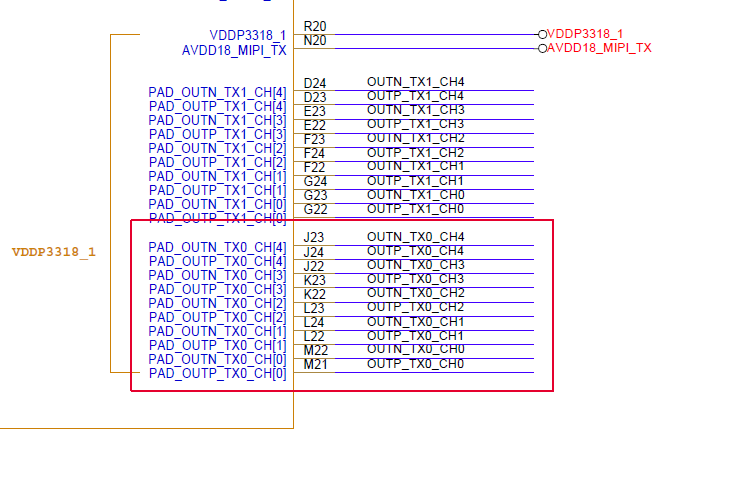

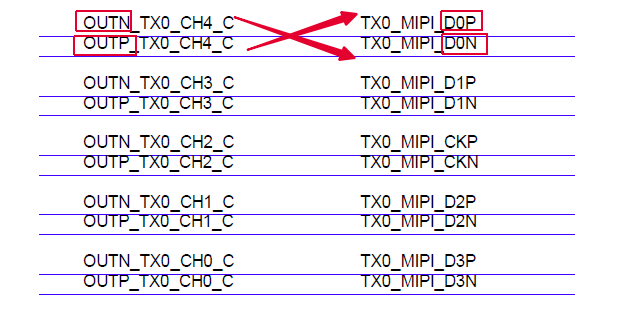

如下图是Demo Board 原理图:

如上图,芯片内部默认情况下对应的pin是:

-

Clk对应的是PAD_OUTN_TX0_CH[2] PAD_OUTP_TX0_CH[2]

-

Lane0对应的是PAD_OUTN_TX0_CH[4] PAD_OUTP_TX0_CH[4]

-

Lane1对应的是PAD_OUTN_TX0_CH[3] PAD_OUTP_TX0_CH[3]

-

Lane2对应的是PAD_OUTN_TX0_CH[1] PAD_OUTP_TX0_CH[1]

-

Lane3对应的是PAD_OUTN_TX0_CH[0] PAD_OUTP_TX0_CH[0]

3.3.1.2. 对应的padmux

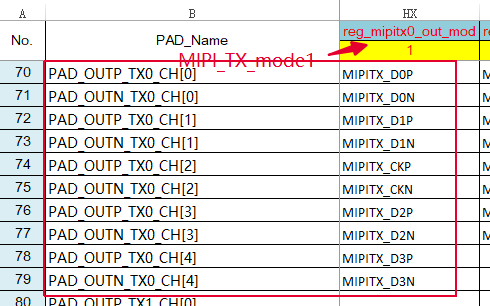

查看SSU 9383 HW CheckList V1.0.xlsx的Tmux页找到管脚对应的padmux,如下:

-

信号管脚

3.3.2. 软件相关¶

3.3.2.1. 配置padmux

通过如上知道panel使用的是mipitx0_out_mode1,对应kernel的pioneer5-ssc028a-s01a_demo-padmux.dtsi(使用的config不一样话对应的padmux.dtsi不一样)配置如下:

3.3.2.2. 配置屏参

-

确认panel规格

HTotal = u16Width + u16HSyncWidth + u16HSyncBackPorch + HSyncFrontPorch VTotal = u16Heigth + u16VSyncWidth + u16VSyncBackPorch + HVyncFrontPorch DCLK = HTotal * VTotal * FPS

-

示例

/ { display-subsystem { panels { RM68200 { compatible = "sstar,panel"; name = "RM68200"; interface = "MIPI"; /* TTL/MIPI/LVDS/BT1120/BT656 */ misc = <&panel_misc>; backlight = <&backlight_mipi>; status = "okay"; port { RM68200_in_mipi: endpoint { remote-endpoint = <&mipi_out_panel>; }; }; panel-timing { clock-frequency = <79000000>; hactive = <720>; hfront-porch = <44>; hback-porch = <60>; hsync-len = <6>; hsync-active = <0>; vactive = <1280>; vfront-porch = <110>; vback-porch = <220>; vsync-len = <40>; vsync-active = <0>; de-active = <0>; pixelclk-active = <0>; }; mipi-params { u8HsTrail = <5>; /* HsTrail */ u8HsPrpr = <3>; /* HsPrpr */ u8HsZero = <5>; /* HsZero */ u8ClkHsPrpr = <10>; /* ClkHsPrpr */ u8ClkHsExit = <14>; /* ClkHsexit */ u8ClkTrail = <3>; /* ClkTrail */ u8ClkZero = <12>; /* ClkZero */ u8ClkHsPost = <10>; /* ClkHsPost */ u8DaHsExit = <5>; /* DaHsexit */ u8ContDet = <0>; /* ConDet */ u8Lpx = <16>; /* Lpx */ u8TaGet = <26>; /* TaGet */ u8TaSure = <24>; /* TaSure */ u8TaGo = <50>; /* TaGo */ u16Bllp = <0>; /* Bllp */ u16Fps = <60>; /* Frame Rate */ enFormat = <3>; /* Output color format, 0:rgb565, 1:rgb666, 2:loosely rgb666, 3:rgb888 */ enCtrl = <1>; /* cotnrol mode, 0:cmd mode, 1:sync pluse, 2:sync event, 3:burst mode */ u8SyncCalibrate = <0>; u16VirHsyncSt = <0>; u16VirHsyncEnd = <0>; u16VsyncRef = <0>; u16DataClkSkew = <7>; enPacketType = <0>; /* Mipidsi command type, 0:DCS mode, 1:generic mode */ mipi-init-cmds = /bits/ 8 < 0xFE 0x01 0x01 0x27 0x01 0x0A 0x29 0x01 0x0A 0x2B 0x01 0xE5 0x24 0x01 0xC0 0x25 0x01 0x53 0x26 0x01 0x00 0x16 0x01 0x52 0x2F 0x01 0x54 0x34 0x01 0x57 0x1B 0x01 0x00 0x12 0x01 0x0A 0x1A 0x01 0x06 0x46 0x01 0x4D 0x52 0x01 0x90 0x53 0x01 0x00 0x54 0x01 0x90 0x55 0x01 0x00 0xFE 0xFE 0xC8 0xFE 0x01 0x03 0x00 0x01 0x05 0x01 0x01 0x16 0x02 0x01 0x09 0x03 0x01 0x0D 0x04 0x01 0x00 0x05 0x01 0x00 0x06 0x01 0x50 0x07 0x01 0x05 0x08 0x01 0x16 0x09 0x01 0x0B 0x0A 0x01 0x0F 0x0B 0x01 0x00 0x0C 0x01 0x00 0x0D 0x01 0x50 0x0E 0x01 0x03 0x0F 0x01 0x04 0x10 0x01 0x05 0x11 0x01 0x06 0x12 0x01 0x00 0x13 0x01 0x54 0x14 0x01 0x00 0x15 0x01 0xC5 0x16 0x01 0x08 0x17 0x01 0x07 0x18 0x01 0x08 0x19 0x01 0x09 0x1A 0x01 0x0A 0x1B 0x01 0x00 0x1C 0x01 0x54 0x1D 0x01 0x00 0x1E 0x01 0x85 0x1F 0x01 0x08 0x20 0x01 0x00 0x21 0x01 0x00 0x22 0x01 0x03 0x23 0x01 0x1F 0x24 0x01 0x00 0x25 0x01 0x28 0x26 0x01 0x00 0x27 0x01 0x1F 0x28 0x01 0x00 0x29 0x01 0x28 0x2A 0x01 0x00 0x2B 0x01 0x00 0x2D 0x01 0x00 0x2F 0x01 0x00 0x30 0x01 0x00 0x31 0x01 0x00 0x32 0x01 0x00 0x33 0x01 0x00 0x34 0x01 0x00 0x35 0x01 0x00 0x36 0x01 0x00 0x37 0x01 0x00 0x38 0x01 0x00 0x39 0x01 0x00 0x3A 0x01 0x00 0x3B 0x01 0x00 0x3D 0x01 0x00 0x3F 0x01 0x00 0x40 0x01 0x00 0x3F 0x01 0x00 0x41 0x01 0x00 0x42 0x01 0x00 0x43 0x01 0x00 0x44 0x01 0x00 0x45 0x01 0x00 0x46 0x01 0x00 0x47 0x01 0x00 0x48 0x01 0x00 0x49 0x01 0x00 0x4A 0x01 0x00 0x4B 0x01 0x00 0x4C 0x01 0x00 0x4D 0x01 0x00 0x4E 0x01 0x00 0x4F 0x01 0x00 0x50 0x01 0x00 0x51 0x01 0x00 0x52 0x01 0x00 0x53 0x01 0x00 0x54 0x01 0x00 0x55 0x01 0x00 0x56 0x01 0x00 0x58 0x01 0x00 0x59 0x01 0x00 0x5A 0x01 0x00 0x5B 0x01 0x00 0x5C 0x01 0x00 0x5D 0x01 0x00 0x5E 0x01 0x00 0x5F 0x01 0x00 0x60 0x01 0x00 0x61 0x01 0x00 0x62 0x01 0x00 0x63 0x01 0x00 0x64 0x01 0x00 0x65 0x01 0x00 0x66 0x01 0x00 0x67 0x01 0x00 0x68 0x01 0x00 0x69 0x01 0x00 0x6A 0x01 0x00 0x6B 0x01 0x00 0x6C 0x01 0x00 0x6D 0x01 0x00 0x6E 0x01 0x00 0x6F 0x01 0x00 0x70 0x01 0x00 0x71 0x01 0x00 0x72 0x01 0x00 0x73 0x01 0x00 0x74 0x01 0x04 0x75 0x01 0x04 0x76 0x01 0x04 0x77 0x01 0x04 0x78 0x01 0x00 0x79 0x01 0x00 0x7A 0x01 0x00 0x7B 0x01 0x00 0x7C 0x01 0x00 0x7D 0x01 0x00 0x7E 0x01 0x86 0x7F 0x01 0x02 0x80 0x01 0x0E 0x81 0x01 0x0C 0x82 0x01 0x0A 0x83 0x01 0x08 0x84 0x01 0x3F 0x85 0x01 0x3F 0x86 0x01 0x3F 0x87 0x01 0x3F 0x88 0x01 0x3F 0x89 0x01 0x3F 0x8A 0x01 0x3F 0x8B 0x01 0x3F 0x8C 0x01 0x3F 0x8D 0x01 0x3F 0x8E 0x01 0x3F 0x8F 0x01 0x3F 0x90 0x01 0x00 0x91 0x01 0x04 0x92 0x01 0x3F 0x93 0x01 0x3F 0x94 0x01 0x3F 0x95 0x01 0x3F 0x96 0x01 0x05 0x97 0x01 0x01 0x98 0x01 0x3F 0x99 0x01 0x3F 0x9A 0x01 0x3F 0x9B 0x01 0x3F 0x9C 0x01 0x3F 0x9D 0x01 0x3F 0x9E 0x01 0x3F 0x9F 0x01 0x3F 0xA0 0x01 0x3F 0xA2 0x01 0x3F 0xA3 0x01 0x3F 0xA4 0x01 0x3F 0xA5 0x01 0x09 0xA6 0x01 0x0B 0xA7 0x01 0x0D 0xA9 0x01 0x0F 0xFE 0xFE 0x0a 0xAA 0x01 0x03 0xFE 0xFE 0x0a 0xAB 0x01 0x07 0xFE 0xFE 0x0a 0xAC 0x01 0x01 0xAD 0x01 0x05 0xAE 0x01 0x0D 0xAF 0x01 0x0F 0xB0 0x01 0x09 0xB1 0x01 0x0B 0xB2 0x01 0x3F 0xB3 0x01 0x3F 0xB4 0x01 0x3F 0xB5 0x01 0x3F 0xB6 0x01 0x3F 0xB7 0x01 0x3F 0xB8 0x01 0x3F 0xB9 0x01 0x3F 0xBA 0x01 0x3F 0xBB 0x01 0x3F 0xBC 0x01 0x3F 0xBD 0x01 0x3F 0xBE 0x01 0x07 0xBF 0x01 0x03 0xC0 0x01 0x3F 0xC1 0x01 0x3F 0xC2 0x01 0x3F 0xC3 0x01 0x3F 0xC4 0x01 0x02 0xC5 0x01 0x06 0xC6 0x01 0x3F 0xC7 0x01 0x3F 0xC8 0x01 0x3F 0xC9 0x01 0x3F 0xCA 0x01 0x3F 0xCB 0x01 0x3F 0xCC 0x01 0x3F 0xCD 0x01 0x3F 0xCE 0x01 0x3F 0xCF 0x01 0x3F 0xD0 0x01 0x3F 0xD1 0x01 0x3F 0xD2 0x01 0x0A 0xD3 0x01 0x08 0xD4 0x01 0x0E 0xD5 0x01 0x0C 0xD6 0x01 0x04 0xD7 0x01 0x00 0xDC 0x01 0x02 0xDE 0x01 0x10 0xFE 0xFE 0xC8 0xFE 0x01 0x04 0x60 0x01 0x00 0x61 0x01 0x0C 0x62 0x01 0x14 0x63 0x01 0x0F 0x64 0x01 0x08 0x65 0x01 0x15 0x66 0x01 0x0F 0x67 0x01 0x0B 0x68 0x01 0x17 0x69 0x01 0x0D 0x6A 0x01 0x10 0x6B 0x01 0x09 0x6C 0x01 0x0F 0x6D 0x01 0x11 0x6E 0x01 0x0B 0x6F 0x01 0x00 0x70 0x01 0x00 0x71 0x01 0x0C 0x72 0x01 0x14 0x73 0x01 0x0F 0x74 0x01 0x08 0x75 0x01 0x15 0x76 0x01 0x0F 0x77 0x01 0x0B 0x78 0x01 0x17 0x79 0x01 0x0D 0x7A 0x01 0x10 0x7B 0x01 0x09 0x7C 0x01 0x0F 0x7D 0x01 0x11 0x7E 0x01 0x0B 0x7F 0x01 0x00 0xFE 0xFE 0xC8 0xFE 0x01 0x0E 0x01 0x01 0x75 0x49 0x01 0x56 0xFE 0xFE 0xC8 0xFE 0x01 0x00 0x58 0x01 0xA9 0x11 0x00 0x00 0xFE 0xFE 0xC8 0x29 0x00 0x00 0xFE 0xFE 0xC8 0xFF 0xFF >; }; }; }; }; }; -

MIPI屏参在配置上会比TTL的稍有差异,主要关注:

-

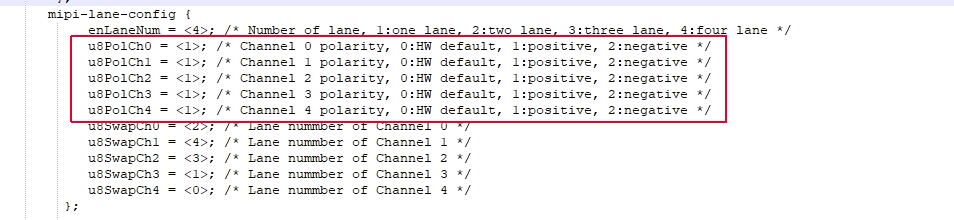

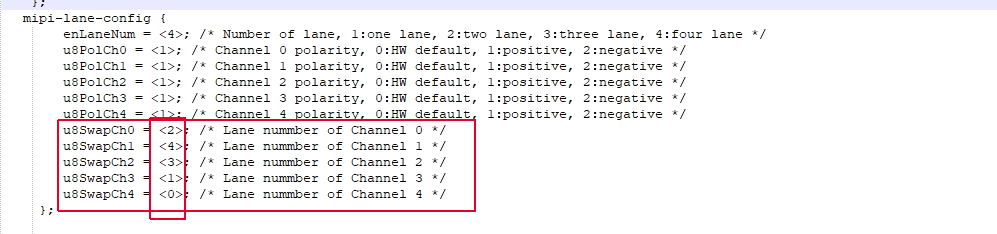

设置各Lane的P/N极性翻转,参考硬件跟Panel的连接确认是否需要翻转即可,如上面原理图:

对应kernel的pioneer5-ssz028a-s01a-m-panel.dtsi(使用的config不一样话对应的panel-misc.dtsi不一样) 配置如下:

-

由原理图可知,panel和soc的连接

Clk对应的是PAD_OUTN_TX0_CH[2] PAD_OUTP_TX0_CH[2]

Lane0对应的是PAD_OUTN_TX0_CH[4] PAD_OUTP_TX0_CH[4]

Lane1对应的是PAD_OUTN_TX0_CH[3] PAD_OUTP_TX0_CH[3]

Lane2对应的是PAD_OUTN_TX0_CH[1] PAD_OUTP_TX0_CH[1]

Lane3对应的是PAD_OUTN_TX0_CH[0] PAD_OUTP_TX0_CH[0]

对应kernel的pioneer5-ssz028a-s01a-m-panel.dtsi(使用的config不一样话对应的panel-misc.dtsi不一样)

配置如下:

-

如示例,panel-timing 部分主要是设置Panel规格书列明的H/V相关参数,参照TTL的方法逐个填入接可

-

mipi-init-cmds 部分主要是Panel的初始化cmd,这部份cmd是各panel厂商参照DSC的标准自定义的,所以cmd一般是找Panel的芯片原厂提供

-

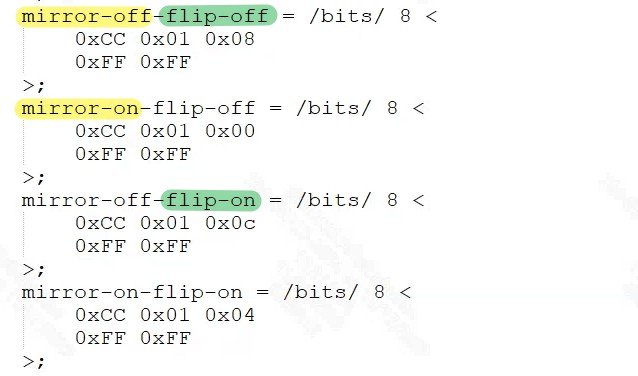

新版本SDK(1.6.24之后),mipi屏添加了屏幕mirror/flip的支持,可通过适当的mipi命令设置屏幕的刷新方向以达到显示左右镜像或上下翻转的效果,可参考

panel-VAO050FHBA01.dts中新增的如下设置项:

我们将

mipi-init-cmds初始化完之后屏幕的状态视为正常无镜像/翻转的状态,因此mirror-off-flip-off命令设置的状态应与初始化完之后的状态一致。用户可根据屏幕实际支持的功能单独配置镜像/翻转状态,即只支持镜像时只配置mirror-off-flip-off、mirror-on-flip-off这两组参数,只支持翻转时只配置mirror-off-flip-off、mirror-off-flip-on这两组参数,同时支持镜像/翻转则四组参数全部设置。

- 以下步骤根据实际SDK版本需要二选一

-

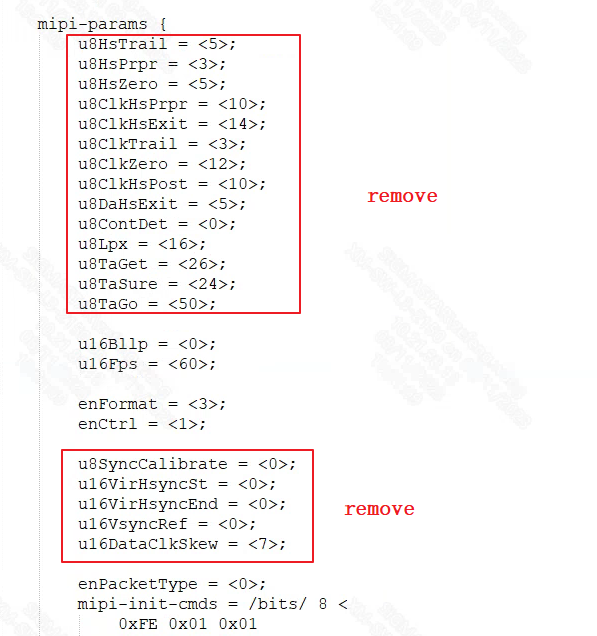

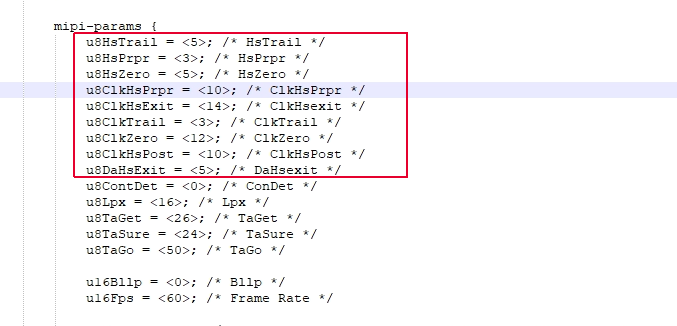

针对新的SDK(1.6.21版本后),MIPI Dphy时序相关配置已经放到了driver去做,原屏参中的部分参数可以直接移除,如下:

-

旧SDK版本(1.6.12版本(包含)之前)需要按照下图配置Dphy参数,这部分主要是对传输过程中时序要求

这部分我们准备了一个通用的Excel表格,只要输入对应Panel的HTotal/VTotal即会自动生成:

示例如下:

红框部分就是按照公式自动生成的参数,在范围内微调对应填到软件屏参即可

-

4. BT601/BT656点屏介绍¶

4.1. 点屏流程¶

BT6xx信号与TTL可归属为同类型的信号,在软件上统一为 并行输出口。有区别的是TTL以RGB格式输出数据,而BT6xx接口以YUV格式输出数据。BT6xx的点屏流程与TTL流程基本一致,除了interface有区别外需设置为正确的类型外(BT601/BT656),其他的屏参基本一致。

5. LVDS点屏介绍¶

5.1. 基本概念¶

LVDS(Low Voltage Differential Signaling)是一种低压差分信号的数字视频信号传输接口。利用非常低的电压摆幅在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

在传输数据的传输方式上可分为以下几类:

-

6位LVDS输出接口,用到3对差分对加一对clock

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或 18bit LVDS接口。

-

双路6位LVDS输出接口,使用两路6位LVDS输出

这种接口电路中,采用双路方式传输,每个基色信号采用6位数据,其中奇路数据为18位,偶路数据为18位, 共36位RGB数据,因此,也称36位或36bit LVDS接口。

-

8位LVDS输出接口,用到4对差分对加一对clock

这种接口电路中,采用单路方式传输,每个基色信号采用8位数据,共24位RGB数据,因此,也称24位或 24bit LVDS接口。

-

双路8位LVDS输出接口,使用两路8位LVDS输出

这种接口电路中,采用双路方式传输,每个基色信号采用8位数据,其中奇路数据为24位,偶路数据为24位, 共48位RGB数据,因此,也称48位或48bit LVDS接口。

-

10位LVDS输出接口,需用到5对差分对加一对clock,暂不支持10bit接口

LVDS数据格式有两种:JEIDA标准、VESA标准。两种标准的区别是数据包中RGB数据的排列方式不同,这里不再深入探讨,相关细节资料可通过互联网获取。

5.2. 点屏流程¶

5.2.1. 硬件相关¶

在当前的evb及demo板设计上lvds channel 0/1与mipi tx1/tx2的硬件接口是复用的,硬件连接如下图:

可以看到LVDS硬件接口与MIPI的硬件接口类似,均是使用几组差分信号分别传输clock跟data。与mipi屏的差异是lvds只需配置正确的timing参数即可,不再需要设置初始化命令,且可以将两路lvds组成双通道(分别输出奇偶场)输出到同一个屏。

如上图,芯片内部默认情况下channel 1对应的pin是(channel 2类似):

Clk对应的是PAD_OUTN_TX0_CH[4] PAD_OUTP_TX0_CH[4]

Lane0对应的是PAD_OUTN_TX0_CH[3] PAD_OUTP_TX0_CH[3]

Lane1对应的是PAD_OUTN_TX0_CH[2] PAD_OUTP_TX0_CH[2]

Lane2对应的是PAD_OUTN_TX0_CH[0] PAD_OUTP_TX0_CH[0]

Lane3对应的是PAD_OUTN_TX0_CH[1] PAD_OUTP_TX0_CH[1]

5.2.2. 软件相关¶

屏参示例:

// 以M270HVN02为例 / { display-subsystem { panels { panel_lvds_misc:panel_lvds_misc { lvds-lane-config { u8Channel = <0>; /* 0:dual_channel 1:channel_1 2:channel_2*/ enLaneNum = <4>; u8ClkLane = <0x63>; u8PolLane0 = <0>; u8PolLane1 = <0>; u8PolLane2 = <0>; u8PolLane3 = <0>; u8PolLane4 = <0>; u8SwapLane0 = <4>; u8SwapLane1 = <3>; u8SwapLane2 = <2>; u8SwapLane3 = <0>; u8SwapLane4 = <1>; }; }; M270HVN02 { compatible = "sstar,panel"; name = "M270HVN02"; interface = "LVDS"; width-mm = <598>; height-mm = <336>; misc = <&panel_lvds_misc>; backlight = <&backlight_lvds>; status = "okay"; port { M270HVN02_in_lvds: endpoint { remote-endpoint = <&lvds_out_panel>; }; }; panel-timing { clock-frequency = <144000000>; hactive = <1920>; hfront-porch = <88>; hback-porch = <148>; hsync-len = <44>; hsync-active = <0>; vactive = <1080>; vfront-porch = <4>; vback-porch = <36>; vsync-len = <5>; vsync-active = <0>; de-active = <0>; pixelclk-active = <0>; }; lvds-params { u8SwapOddEven = <0>; u8SwapML = <0>; enFormat = <0>; }; }; }; }; };

屏参介绍(仅介绍LVDS屏参中新增的部分):

| 参数 | 描述 |

|---|---|

| u8SwapOddEven | 奇偶(通道½)通道交换 |

| u8SwapML | RGB数据高低位交换 |

| enFormat | 数据格式,0-VESA、1-JEIDA |

| lvds-lane-config | lvds lane配置节点 |

| u8Channel | lvds通道号,0-双通道、1-通道1、2-通道2 |

| enLaneNum | 使用的lane数,目前仅支持3lane(6bit格式)/4lane(8bit格式) |

| u8ClkLane | 设置为0x63即可 |

| u8PolLane0 | 差分对0极性(是否交换P/N) |

| u8PolLane1 | 差分对1极性(是否交换P/N) |

| u8PolLane2 | 差分对2极性(是否交换P/N) |

| u8PolLane3 | 差分对3极性(是否交换P/N) |

| u8PolLane4 | 差分对4极性(是否交换P/N) |

| u8SwapLane0 | Clock lane使用的差分对号 |

| u8SwapLane1 | Lane0使用的差分对号 |

| u8SwapLane2 | Lane1使用的差分对号 |

| u8SwapLane3 | Lane2使用的差分对号 |

| u8SwapLane4 | Lane3使用的差分对号 |