UART Reference

1. Overview¶

SSD20X provides 4 groups of uart (including a group of fuart), the pin corresponding to each MODE is as follows:

| UART MODE | RX | TX | CTS | RTS |

|---|---|---|---|---|

| UART0 | PM_UART_RX | PM_UART_TX | NA | NA |

| UART1 | PAD_UART1_RX | PAD_UART1_TX | NA | NA |

| UART2 | PAD_GPIO8 | PAD_GPIO9 | NA | NA |

| FUART(Without flow control) | PAD_FUART_RX | PAD_FUART_TX | NA | NA |

| FUART(With flow control) | PAD_FUART_RX | PAD_FUART_TX | PAD_FUART_CTS | PAD_FUART_RTS |

2. UART Config¶

2.1. Config in Kernel¶

The main config is padmux.

2.2. Configure Padmode¶

-

Add padmux settings, open

kernel\arch\arm\boot\dts\infinity2m-ssc010a-s01a-padmux-display.dtsiFUART(With flow control): when using MODE1, the default baud is 9600

<PAD_FUART_RX PINMUX_FOR_FUART_MODE_1 MDRV_PUSE_FUART_RX>, <PAD_FUART_TX PINMUX_FOR_FUART_MODE_1 MDRV_PUSE_FUART_TX>, <PAD_FUART_CTS PINMUX_FOR_FUART_MODE_1 MDRV_PUSE_FUART_CTS>, <PAD_FUART_RTS PINMUX_FOR_FUART_MODE_1 MDRV_PUSE_FUART_RTS>,

FUART(Without flow control): when using MODE2, the default baud is 9600 // /dev/ttyS2

<PAD_FUART_RX PINMUX_FOR_FUART_MODE_2 MDRV_PUSE_FUART_RX>, <PAD_FUART_TX PINMUX_FOR_FUART_MODE_2 MDRV_PUSE_FUART_TX>,

Configure uart0: the default baud is 115200 // /dev/ttyS0

<PM_UART_RX PINMUX_FOR_UART0_MODE_1 MDRV_PUSE_UART0_RX >, <PM_UART_TX PINMUX_FOR_UART0_MODE_1 MDRV_PUSE_UART0_TX >,

Configure uart1: the default baud is 9600 // /dev/ttyS1

<PAD_UART1_RX PINMUX_FOR_UART1_MODE_1 MDRV_PUSE_UART1_RX>, <PAD_UART1_TX PINMUX_FOR_UART1_MODE_1 MDRV_PUSE_UART1_TX>,

Configure uart2: the default baud is 9600 // /dev/ttyS3

<PAD_GPIO8 PINMUX_FOR_UART2_MODE_2 MDRV_PUSE_UART2_RX>, <PAD_GPIO9 PINMUX_FOR_UART2_MODE_2 MDRV_PUSE_UART2_TX>,

After that, recompile the kernel and replace the kernel image to project to burn.

3. Use Uart¶

3.1. Confirm /dev/ttySx Used By Uart Pin¶

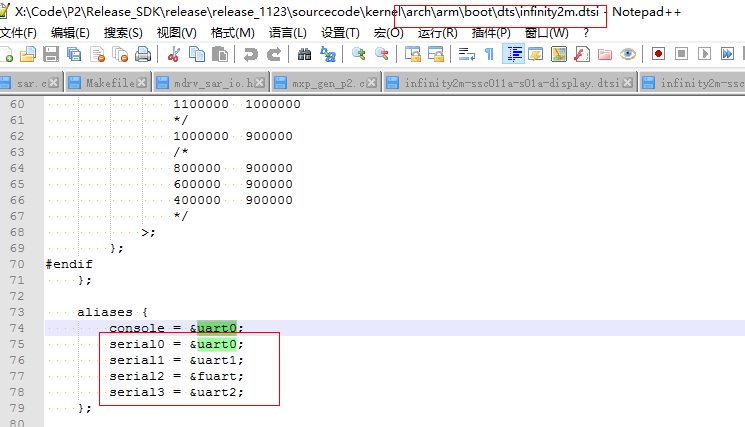

Check the dts to confirm which serialx the uart corresponds to.

Serialx corresponds to /dev/ttySx.

Fig 3-1 Check serialx

3.2. Use Application Layer¶

Refer to the following link for application layer usage:

https://blog.csdn.net/aaron_111/article/details/84876508

4. Uart Driver Architecture and debug¶

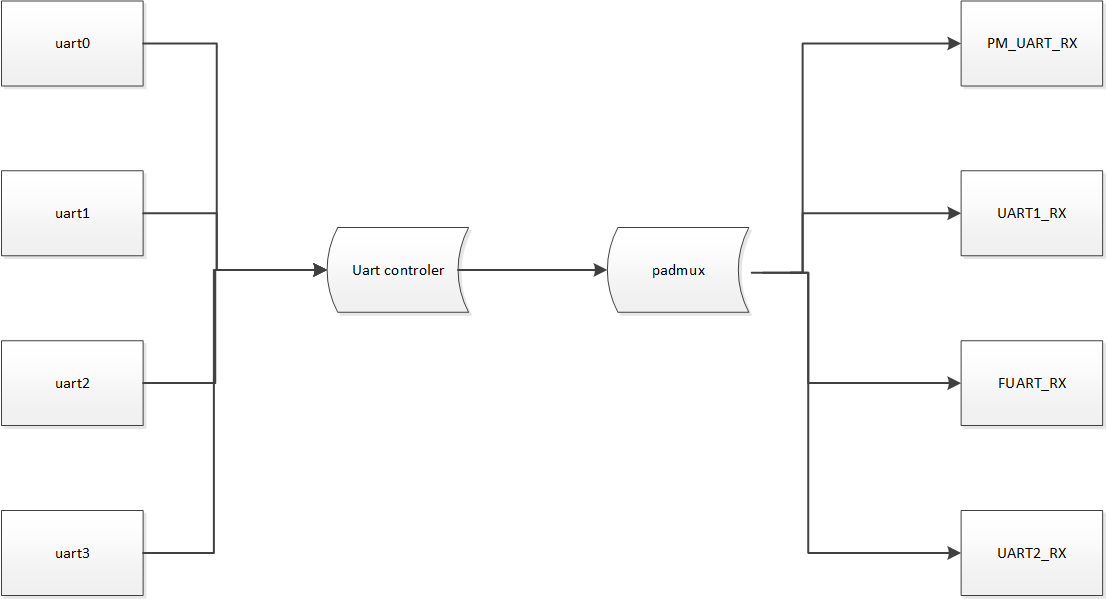

Figure 4-1 Uart driver framework

It can be seen from the above figure that the driver is mainly connected to the uart controller and the corresponding pad in series.

The following registers can be used to determine whether the corresponding uart controller and padmux are connected in series:

-

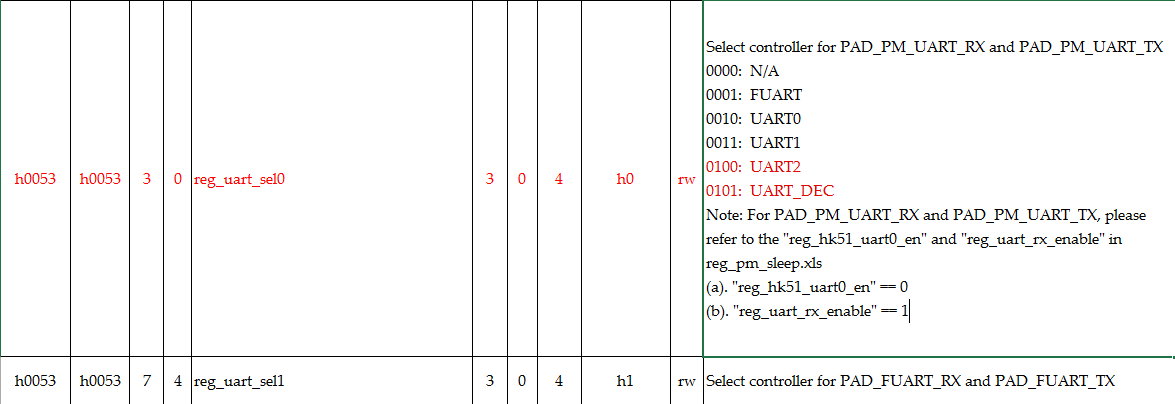

Uart controller

0x101e 0x53(16bit)

Figure 4-2

Figure 4-3

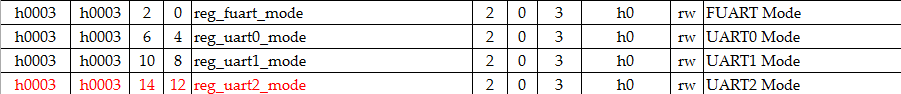

-

Padmux

0x101e 0x03(16bit)

Figure 4-4