I2c_DebugSop

REVISION HISTORY¶

| Revision No. | Description |

Date |

|---|---|---|

| 1.0 | 12/13/2024 |

问题一:I2C通信失败,无法抓到时序¶

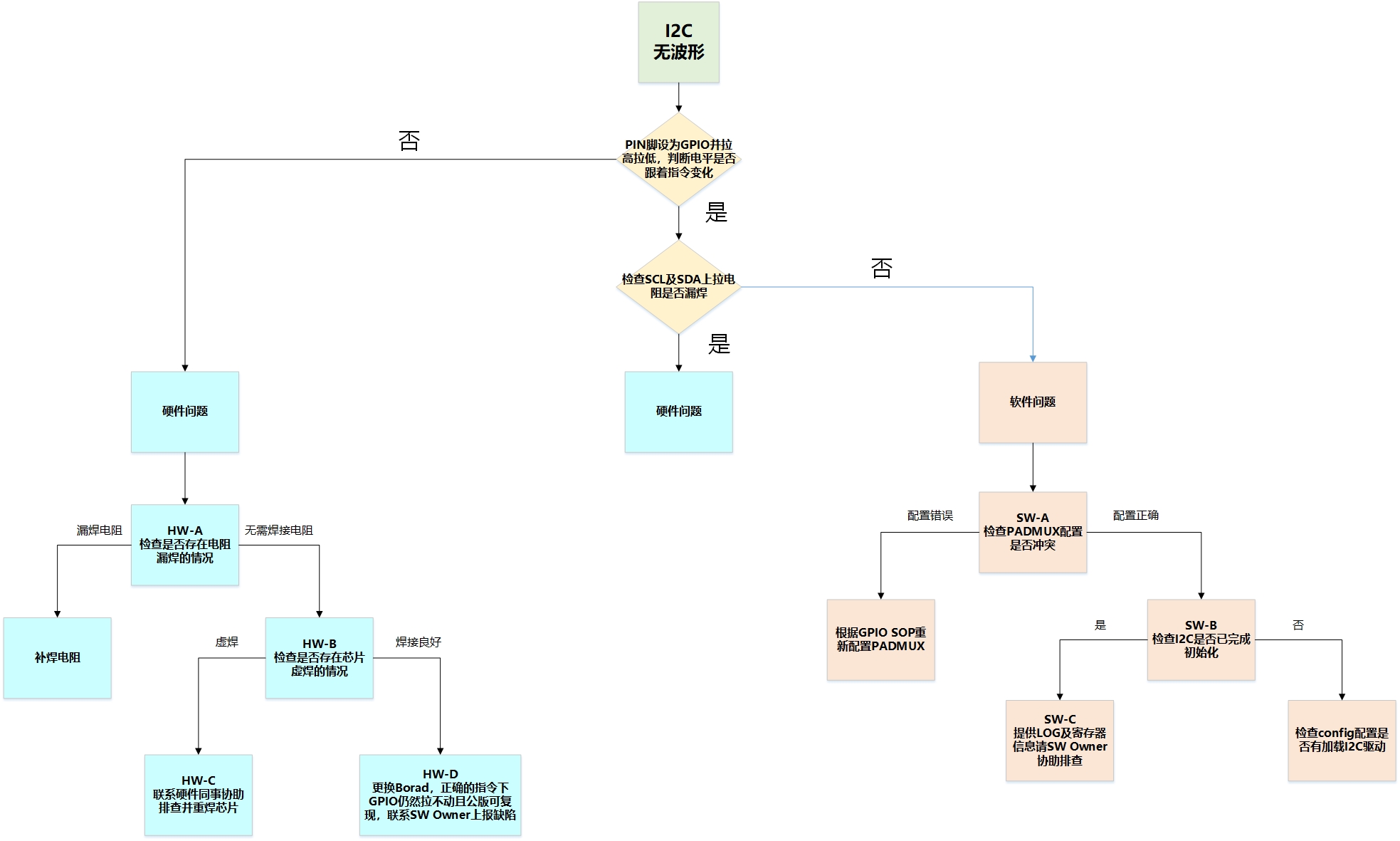

1. I2C无波形问题的Debug流程图¶

2. I2C无波形问题的Debug流程说明¶

2.1 硬件问题¶

检查到I2C无输出波形时,可操作寄存器将对应PIN脚设为GPIO并拉高拉低(请注意某些PIN脚GPIO功能优先级并不是最高的,此时需要先清除更高优先级),如果实际输出电平没有变化,则可判断为硬件问题,可按照如下顺序排查:

2.1.1 HW-A 检查电阻¶

查看原理图的对应PIN脚是否有电阻漏焊,漏焊则需要补焊电阻,否则PIN脚不通

2.1.2 HW-B 检查焊接情况¶

如果更换Board后,GPIO是可以拉高拉低的,那么可能是芯片虚焊,需要rework

2.1.3 HW-C 请求协助¶

联系硬件同事协助排查并重焊芯片

2.1.4 HW-D 缺陷上报¶

如果更换Board后,GPIO仍然无法拉高拉低,联系FAE上报缺陷

2.2 判断SCL及SDA上拉电阻是否漏焊¶

SCL及SDA两PIN脚切换成GPIO可正常拉高拉低的情况下,切回I2C MODE后IDLE电平为低电平,需要检查上拉电阻是否漏焊

2.3 软件问题¶

2.3.1 步骤SW-A 检查PADMUX¶

检查PADMUX是否存在冲突,详见Gpio_DebugSop中的PADMUX冲突检查内容

2.3.2 步骤SW-B 检查I2C初始化情况¶

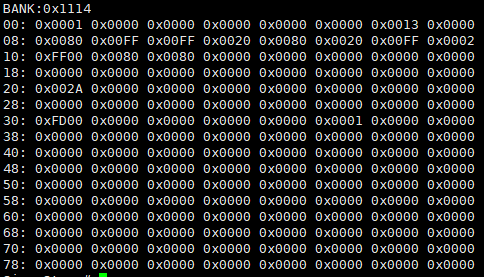

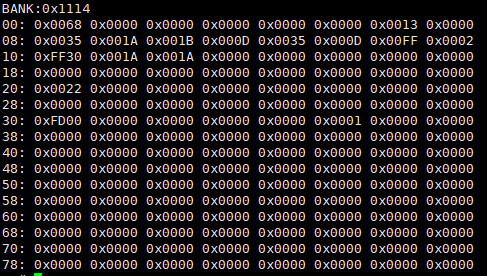

dump i2c bank,可通过寄存器状态判断I2C是否已完成初始化,主要查看offset 0x00数值是否不为0x1

i2c0处于未初始化时Bank信息如下【以下bank信息以I2C0为例】:

i2c0已完成初始化后Bank信息如下:

| BUS | BANK | PADMUX BANK | Offset |

|---|---|---|---|

| MIIC0 | 0x1114 | 0x103c | 0x6f #[2:0] |

| MIIC1 | 0x1115 | 0x103c | 0x53 #[2:0] |

| MIIC2 | 0x1116 | 0x103c | 0x3f #[13:12] |

| MIIC3 | 0x1117 | 0x103c | 0x73 #[2:0] |

| MIIC4 | 0x1118 | 0x103c | 0x3f #[13:12] |

| PM_MIIC | 0x3E | 0x0E | 0x50 #0 |

其他I2C bank信息见上表。

如若未完成初始化,自然无法输出I2C波形,请检查config及DTS配置是否有加载I2C驱动

Linux config:

Device Drivers --->

I2C support --->

<*> I2C device interface

SStar SoC platform drivers --->

<*> Sstar I2C driver

Linux DTS:

i2c0: i2c@1f222800 { //选择bus

compatible = "sstar,i2c";

reg = <0x1F222800 0x200>;

......

status = "ok"; //ok:初始化i2c

};

2.2.4 步骤SW-C 请求协助¶

上述步骤SW-A,SW-B均检查OK,请提供I2C相关报错的LOG以及I2C BANK信息(0x103c、0x1114(i2c0为例)、0x1038),联系FAE 协助 debug

问题二:从设备与I2C通信出现NACK现象¶

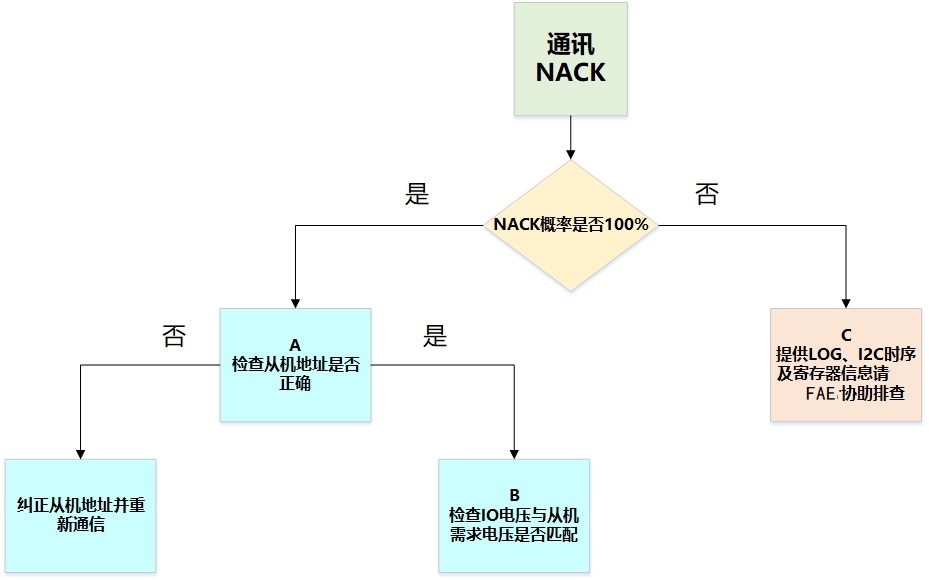

1. I2C通讯NACK问题的Debug流程图¶

2. I2C通讯NACK问题的Debug流程说明¶

2.1 步骤A 检查从机地址¶

目前I2C通讯传参使用的从机地址都是未偏移的地址,驱动会自动将收到的从机地址左移一位后触发通讯,请注意不要传入偏移后的地址

2.2 步骤B 检查电压¶

SCL及SDA的上拉电压与从机需求电压不匹配的情况下,SCL及SDA的电压无法达到从机需求,那么抓到的时序一般表现为发送从设备地址后就会收到NACK信号

2.3 步骤C 请求协助¶

上述步骤SW-A,SW-B均检查OK,请提供I2C相关LOG、I2C时序、及I2C BANK信息,联系FAE debug

问题三:I2C各种不规则时序问题¶

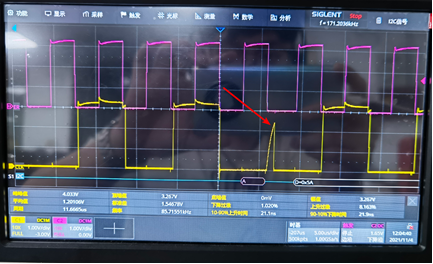

1. 阻抗不匹配带来的过冲现象¶

阻抗不匹配需要rework硬件,否则会直接导致信号的反射,反射信号与原始信号叠加,就会产生过冲、回沟、台阶等信号完整性问题,如下图所示:

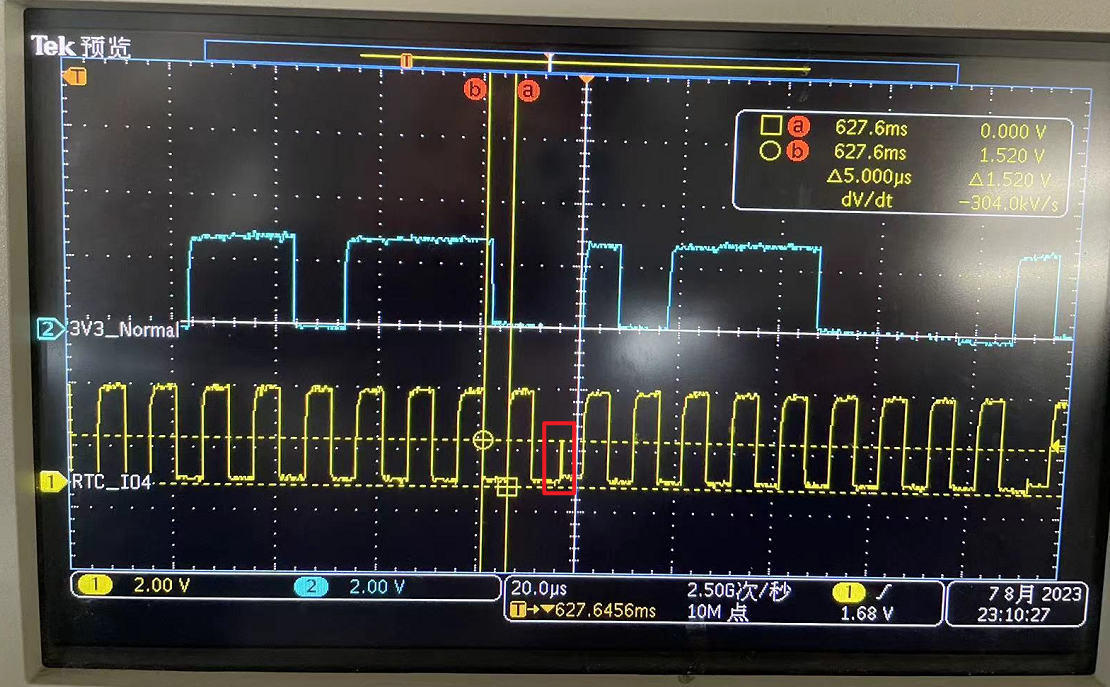

2. SCL产生不符合标准时序的短脉冲¶

涉及I2C时序在上升沿状态的相关问题时,往往与I2C推挽和开漏输出的设定有关, 通常表现为push high较慢,SCL上升沿有陡坡,或者抓到不符合时序的短脉冲等

上图现象是SCL使用one push功能,半高电平是one push造成,正常会继续push high,但有些硬件外部干扰较强,one push后无法继续推高,反而回落造成短脉冲,可以通过操作寄存器直接取消one push功能,比如I2C bus0:

I2C0 Bank = 0x1114, offset = 0x00, bit[6] = 0

3. SDA产生不符合标准时序的短脉冲¶

当主机收到从机ack信号后,继续输出下一个bit时,PAD需要从输入模式转换为输出模式,此期间PAD内部上拉电阻产生了短脉冲,正常不影响通讯