PANEL开发参考

1. 概述¶

本文档主要的内容是DISP模块在LCD输出场景下的使用说明,让显示相关应用开发人员了解显示驱动的接口及使用流程,了解显示模块功能及使用限制,并介绍了相关调试方法和问题排查手段。

2. 模块介绍¶

2.1. 模块功能介绍¶

-

支持两个video layer,layer0支持4 windows 拼图,layer1 单个window作为PIP使用

-

单个window scaling up

-

单个window crop

-

支持以video layer为单位做rotate 90/270

-

video pixel format支持NV12

-

支持Contrast、Hue、Luma、Saturation、Sharpness、Gamma等图像PQ调整

-

支持SSC,有效减低EMI

-

支持LCD显示(包括TTL PANEL、MIPI PANEL),TTL输出CLK支持范围9Mhz-75Mhz,MIPI DSI输出CLK, 支持范围100Mbps/lane – 1.5Gbps/lane

2.2. 模块源码文件介绍¶

-

alkaid/sdk/interface/inclue/disp/mi_disp.h

声明DISP所有的用户调用API,定义了DISP API当前的version num

-

alkaid/sdk/interface/inclue/disp/mi_disp_datatype.h

定义了DISP API使用到的数据结构类型

-

alkaid/sdk/interface/src/disp/disp_api.c

DISP API实现,最终编译生成libmi_disp.so libmi_disp.a

3. 模块功能¶

3.1. 多路拼图¶

DISP video layer0硬件有4个mgwin,软件抽象为4个input port,可以接收前端输出的yuv数据(NV12),4个input port在video layer0上的显示位置可以任意设置,但4个input port的显示位置不能相互叠加。

图3-1

3.2. PIP¶

DISP video layer1可以用于PIP,将画面叠加到video layer0显示,默认video layer1显示优先级高于video layer0,即如果两个video layer上都有内容,那么video layer1显示在上,video layer0显示在下。

图3-2

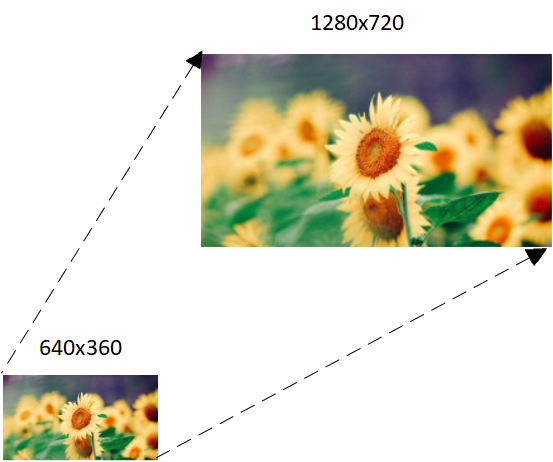

3.3. 图像缩放¶

DISP支持针对单个input port做scaling up,H/V方向放大比例可以达到16倍,来满足每个window对最终显示尺寸的需求。

图3-3

-

相关API:

MI_S32 MI_DISP_SetInputPortAttr(MI_DISP_LAYER DispLayer, MI_DISP_INPUTPORT LayerInputPort, const MI_DISP_InputPortAttr_t *pstInputPortAttr); -

DispLayer

可以使用任意一个video layer上的任意一个input port做scaling up,video layer使用范围0-1

-

LayerInputPort

可以使用任意一个input port做scaling up。如果使用video layer0,input port使用范围0-3;如果使用video layer1,则只有一个input port可以使用。

-

pstInputPortAttr

typedef struct MI_DISP_VidWin_Rect_s { ¦ MI_U16 u16X; ¦ MI_U16 u16Y; ¦ MI_U16 u16Width; ¦ MI_U16 u16Height; } MI_DISP_VidWinRect_t; typedef struct MI_DISP_InputPortAttr_s { ¦ MI_DISP_VidWinRect_t stDispWin; ¦ MI_U16 u16SrcWidth; ¦ MI_U16 u16SrcHeight; } MI_DISP_InputPortAttr_t;

定义input port属性

u16SrcWidth:input image width u16SrcHeight:input image height

u16X:在layer上的显示位置H方向偏移

u16Y:在layer上的显示位置V方向偏移

u16Width:放大后图像显示的宽,不放大等于u16SrcWidth

u16Height:放大后图像显示的高,不放大等于u16SrcHeight

同样如多路拼图所述,放大后的各个window之间不能叠加。

video layer size需要等于最终输出timing的有效width/height,图像才能全屏显示。比如,现在使用一个1920x1080的panel显示,那么输出timing的有效width等于1920,height等于1080,如果只开启了一个input port并且希望该port全屏显示,那么应该满足:

u16Width = video layer width u16Height = video layer height video layer width = panel active width video layer height = panel active height

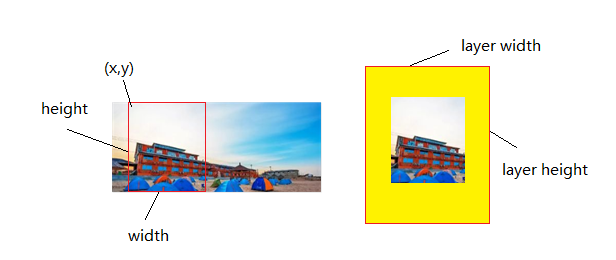

3.4. 图像裁剪¶

DISP支持对input image做crop,适用于zoom in场景,需要对局部区域放大显示。

图3-4

-

相关API:

MI_S32 MI_DISP_SetZoomInWindow(MI_DISP_LAYER DispLayer, MI_DISP_INPUTPORT LayerInputPort, MI_DISP_VidWinRect_t* pstZoomRect); -

DispLayer

可以对任意video layer上的任意input port做crop,layer id取值范围0-1

-

LayerInputPort

可以对任意input port做crop,如果使用video layer0,input port取值范围0-3,如果使用video layer1,则只有一个port可以使用。

-

pstZoomRect

typedef struct MI_DISP_VidWin_Rect_s { ¦ MI_U16 u16X; ¦ MI_U16 u16Y; ¦ MI_U16 u16Width; ¦ MI_U16 u16Height; } MI_DISP_VidWinRect_t;

设定crop属性:

u16X:crop H方向起始点 u16Y:crop V方向起始点 u16Width:crop width u16Height:crop height

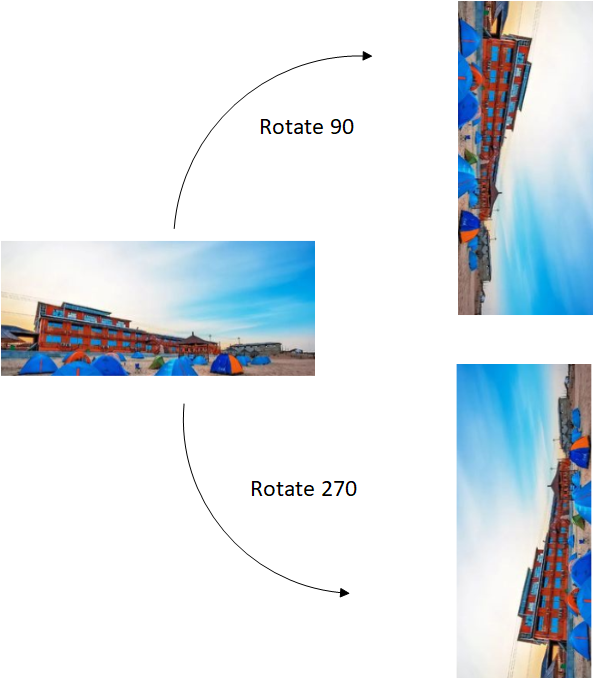

3.5. 图像旋转¶

DISP支持以layer为单位做旋转90度或者270度,同时支持旋转加放大,以满足旋转后需要满屏显示的场景。

图3-5

相关API:

MI_S32 MI_DISP_SetVideoLayerRotateMode(MI_DISP_LAYER DispLayer, MI_DISP_RotateConfig_t *pstRotateConfig);

-

DispLayer

可以使用任意一个video layer做旋转,video layer取值范围0-1

-

pstRotateConfig

typedef enum { ¦ E_MI_DISP_ROTATE_NONE, ¦ E_MI_DISP_ROTATE_90, ¦ E_MI_DISP_ROTATE_180, ¦ E_MI_DISP_ROTATE_270, ¦ E_MI_DISP_ROTATE_NUM, }MI_DISP_RotateMode_e; typedef struct MI_DISP_RotateConfig_s { ¦ MI_DISP_RotateMode_e eRotateMode; }MI_DISP_RotateConfig_t;

设置旋转角度,E_MI_DISP_ROTATE_90旋转90度,E_MI_DISP_ROTATE_270旋转270度,不支持旋转180度。

3.6. SSC¶

时钟展频通过频率调制的手段将集中在窄频带范围内的能量分散到设定的宽频带范围,通过降低时钟在基频和奇次谐波频率的幅度(能量),达到降低系统电磁辐射峰值的目的。

图3-6

SSC在屏参中配置,SSC step/span 由展频计算表中的公式来计算得到。

3.7. PQ¶

3.7.1. xMatrix¶

DISP支持通过3x3 CSC Matrix调节图像Contrast、Hue、Luma、Saturation、Sharpness。

相关API:

MI_S32 MI_DISP_IMPL_SetLcdParam(MI_DISP_DEV DispDev, MI_DISP_LcdParam_t *pstLcdParam)

-

DispDev

DISP设备ID设为0

-

pstLcdParam

typedef struct MI_DISP_Csc_s { ¦ MI_DISP_CscMattrix_e eCscMatrix; /* eCscMatrix 使用第4组Matrix*/ ¦ MI_U32 u32Luma; /* luminance: 0 ~ 100 default: 50 */ ¦ MI_U32 u32Contrast; /* contrast: 0 ~ 100 default: 50 */ ¦ MI_U32 u32Hue; /* hue: 0 ~ 100 default: 50 */ ¦ MI_U32 u32Saturation; /* saturation: 0 ~ 100 default: 40 */ } MI_DISP_Csc_t; typedef struct MI_DISP_LcdParam_s { ¦ MI_DISP_Csc_t stCsc; ¦ MI_U32 u32Sharpness; } MI_DISP_LcdParam_t;

3.7.2. Color Temperature¶

DISP支持图像R/G/B分量的色温调节。

相关API:

MI_S32 MI_DISP_DeviceSetColorTempeture(MI_DISP_DEV DispDev, MI_DISP_ColorTemperature_t

-

DispDev

DISP设备ID设为0

-

pstColorTempInfo

typedef struct { ¦ MI_U16 u16RedOffset; ¦ MI_U16 u16GreenOffset; ¦ MI_U16 u16BlueOffset; ¦ MI_U16 u16RedColor; // 00~FF, 0x80 is no change ¦ MI_U16 u16GreenColor;// 00~FF, 0x80 is no change ¦ MI_U16 u16BlueColor; // 00~FF, 0x80 is no change }MI_DISP_ColorTemperature_t;

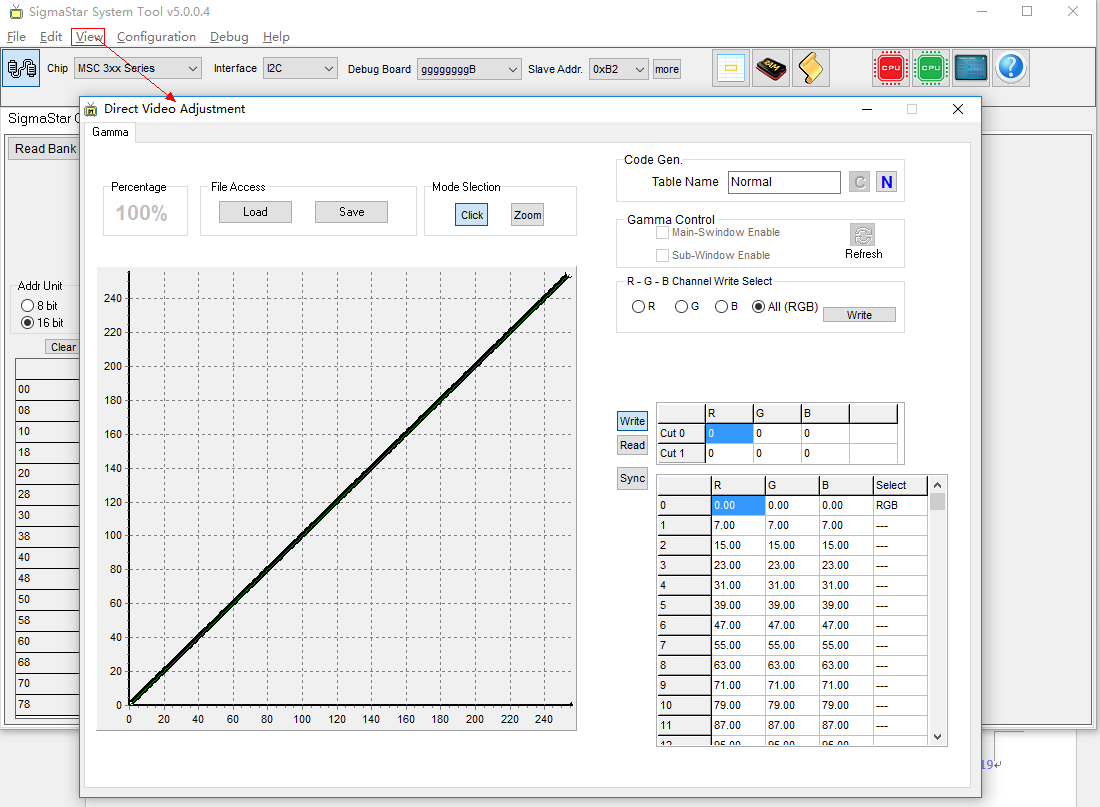

3.7.3. Gamma¶

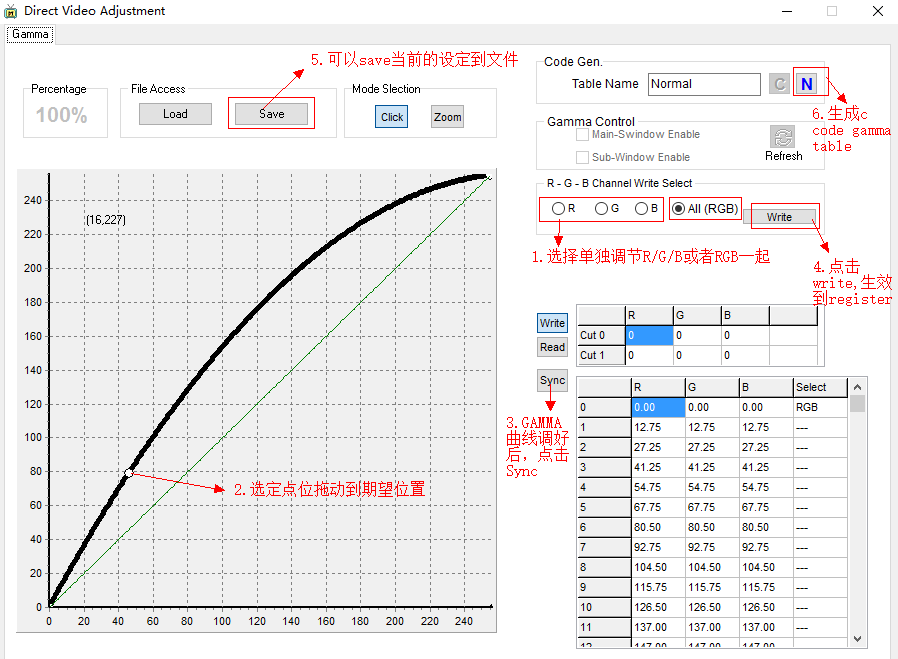

方法一:使用SigmaStar System Tool调GAMMA,参考以下步骤:

-

连接到chip

图3-7

-

打开GAMMA调整界面

图3-8

-

GAMMA调节

图3-9

-

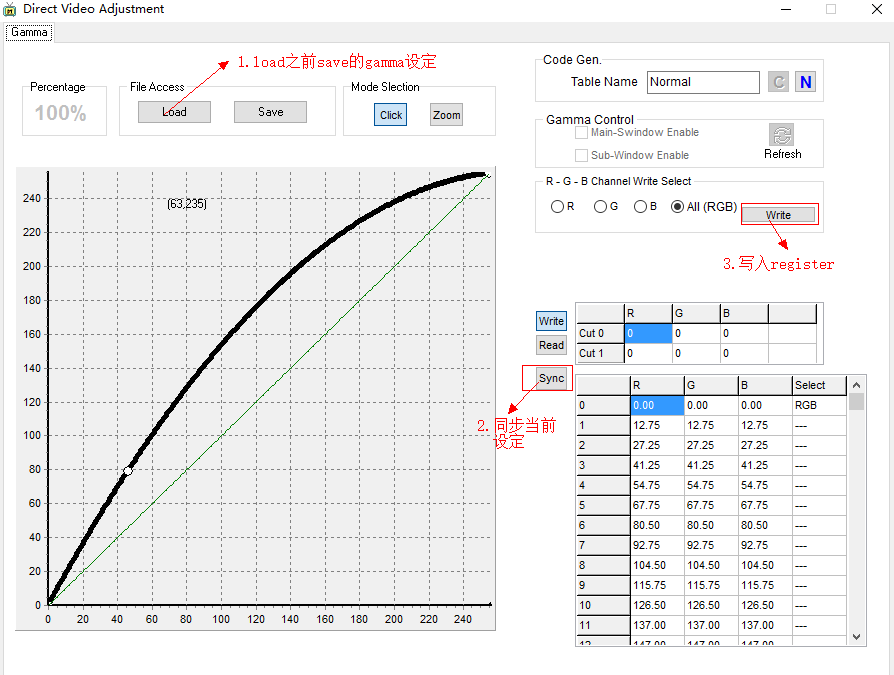

load gamma设定

图3-10

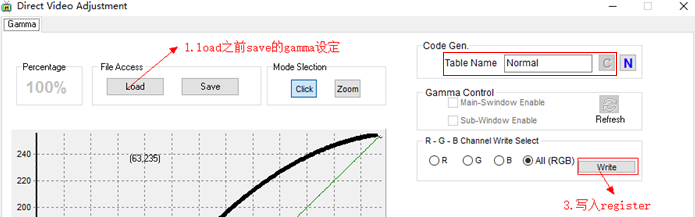

方法二:使用DISP API设定GAMMA

可以将调好的gamma设定通过SigmaStar System Tool生成c code gamma table。

图3-11

SigmaStar System Tool可以生成如下格式的c code gamma table

MI_U8 tnormalGammaR[] = { ¦ 0x00,0x07,0x0F,0x17, ¦ 0x1F,0x27,0x2F,0x37, ¦ 0x3F,0x47,0x4F,0x57, ¦ 0x5F,0x67,0x6F,0x77, ¦ 0x7F,0x87,0x8F,0x97, ¦ 0x9F,0xA7,0xAF,0xB7, ¦ 0xBF,0xC7,0xCF,0xD7, ¦ 0xDF,0xE7,0xEF,0xF7, ¦ 0xFF }; MI_U8 tnormalGammaG[] = { ¦ 0x00,0x07,0x0F,0x17, ¦ 0x1F,0x27,0x2F,0x37, ¦ 0x3F,0x47,0x4F,0x57, ¦ 0x5F,0x67,0x6F,0x77, 0x7F,0x87,0x8F,0x97, ¦ 0x9F,0xA7,0xAF,0xB7, ¦ 0xBF,0xC7,0xCF,0xD7, ¦ 0xDF,0xE7,0xEF,0xF7, ¦ 0xFF }; MI_U8 tnormalGammaB[] = { ¦ 0x00,0x07,0x0F,0x17, ¦ 0x1F,0x27,0x2F,0x37, ¦ 0x3F,0x47,0x4F,0x57, ¦ 0x5F,0x67,0x6F,0x77, ¦ 0x7F,0x87,0x8F,0x97, ¦ 0x9F,0xA7,0xAF,0xB7, ¦ 0xBF,0xC7,0xCF,0xD7, ¦ 0xDF,0xE7,0xEF,0xF7, ¦ 0xFF };

调用DISP API设定GAMMA

MI_DISP_GammaParam_t stGammaParam; stGammaParam.bEn = TRUE; stGammaParam.u16EntryNum = sizeof(tnormalGammaR); stGammaParam.pu8ColorR = tnormalGammaR; stGammaParam.pu8ColorG = tnormalGammaG; stGammaParam.pu8ColorB = tnormalGammaB; MI_DISP_DeviceSetGammaParam(devid, &stGammaParam);

3.8. 输出设备¶

DISP支持LCD以及HDMI/VGA,LCD和HDMI/VGA不能同时显示,HDMI/VGA可以同时输出显示。LCD支持TTL PANEL和MIPI PANEL。本节主要介绍点亮TTL或MIPI PANEL的相关操作。

DISP视频显示数据流程框图如下:

图3-12

DISP video layer0 的4个input port可以绑定vdec的4个channel做4windows拼图显示,DISP video layer1的port可以做PIP使用,即最终video layer1和video layer0做mixer,video layer1显示优先级高于video layer0。

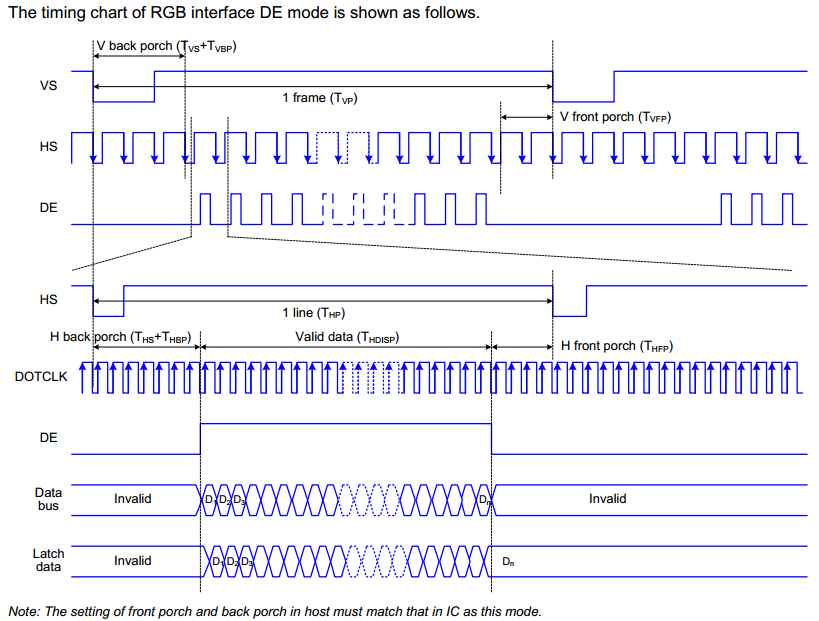

DISP硬件拼图后根据用户选择的输出设备,将拼图后的视频数据按照一定的时序通过TTL接口送出RGB data;如果是MIPI接口,支持sync mode、sync event mode、burst mode等MIPI标准传输模式。

GUI FB/Cursor 有独立的HW engine,需要操作FB device来进行UI的绘制,这部分不做详细介绍。

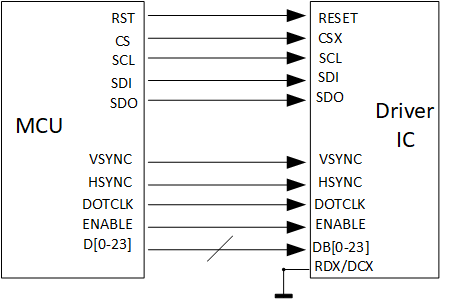

3.8.1. TTL¶

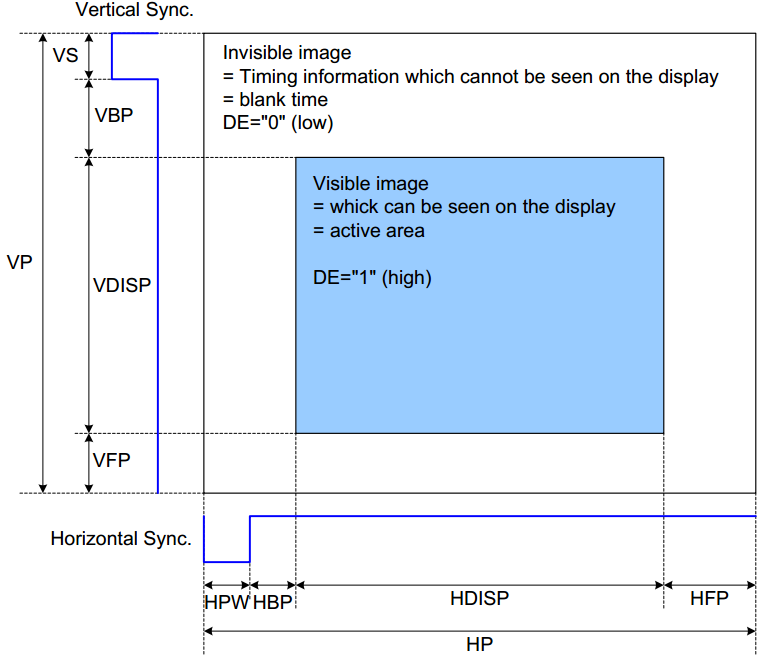

Parallel RGB Interface有两种,DE mode和HV mode,当使能DE的时候,会使用VSYNC、HSYNC、DOTCLK、DE、D[0-23]这些pin,当使能HV mode的时候,会使用VSYNC、HSYNC、DOTCLK、D[0-23]。

图3-13

一些panel driver IC需要对其初始化,其实就是对其内部register的设定,一般会通过SPI或者IIC接口来通信,初始化需要的cmd和data一般由屏厂提供,发送时的数据格式需要参考panel datasheet。

使用Parallel RGB Interface的panel需要HSYNC、VSYNC、DOTCLK来作为同步信号,RGB data只在timing的特定区间有效。

图3-14

行场信号中的blanking区间是不可见区域,只有active区间的RGB data才会最终显示出来,不同的panel Driver IC对于blanking区间的要求不同。

行信号中:

Htotal = HSYNC + HBP + HFP + H Active

场信号中:

Vtotal = VSYNC + VBP + VFP + V Active

最后计算像素时钟频率:

Pixel CLK = Htotal * Vtotal * fps

屏参中时序相关的配置主要是调整行信号中HSYNC、HBP、HFP和场信号中VSYNC、VBP、VFP。panel spec中会提供blanking区间各部分的长度要求。

blanking区间是一个可调范围,最终计算出的pixel clk也是在一个范围内。

主控芯片一般会有时钟频率的限制,所以在点一个新的panel时,应先计算panel的pixel clk,如果将要点的panel满足像素时钟频率的要求,则一般可以点起来。

图3-15 Parallel RGB Interface Timing

3.8.2. MIPI¶

MIPI DSI 规格:

-

1-4 data lanes, 1 clock lane

-

Level:

-

LP: 0~12V

-

HS: 100~300mV,

-

-

HS: 80Mbps ~ 1.5Gbps/lane

-

Pixel format:

-

16 bpp (5,6,5 RGB) each pixel using two bytes

-

18 bpp (6,6,6 RGB) packed

-

18 bpp (6, 6, 6 RGB) loosely packed into three bytes

-

24 bpp (8, 8, 8 RGB), each pixel using three bytes

-

-

video mode: BURST_MODE/SYNC_EVENT/SYNC_PULSE

-

data/clk chn swap

-

data/clk chn P/N swap

-

data clk skew adjustment

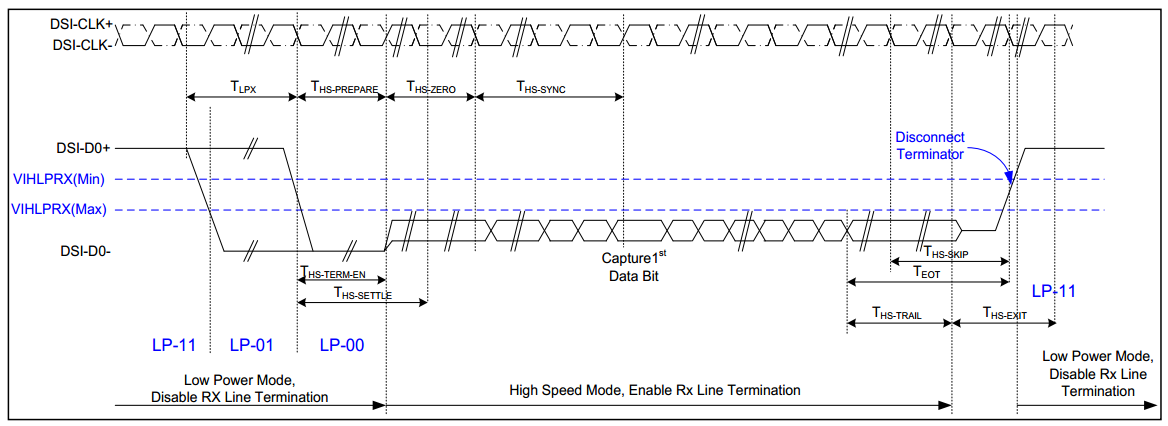

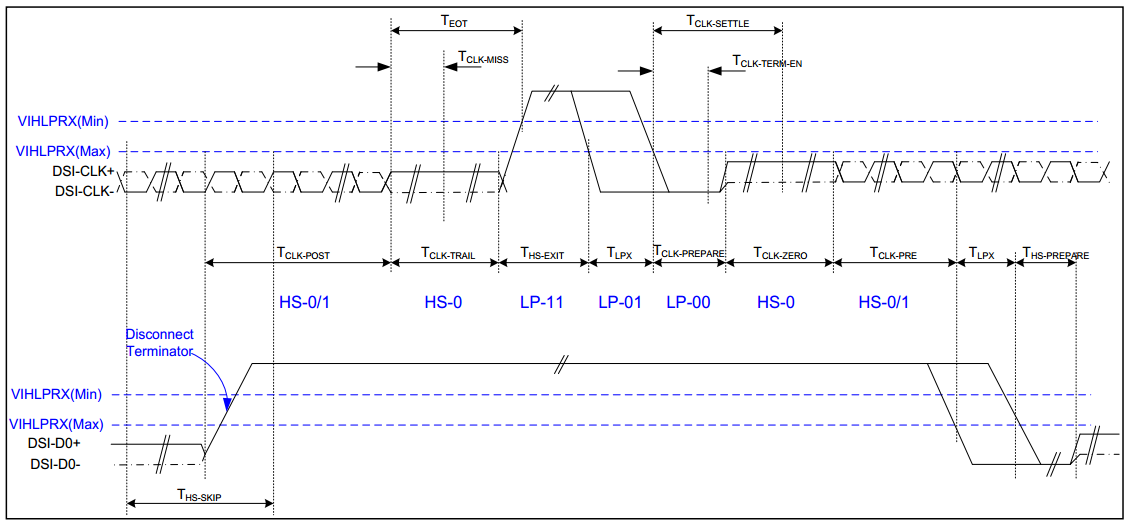

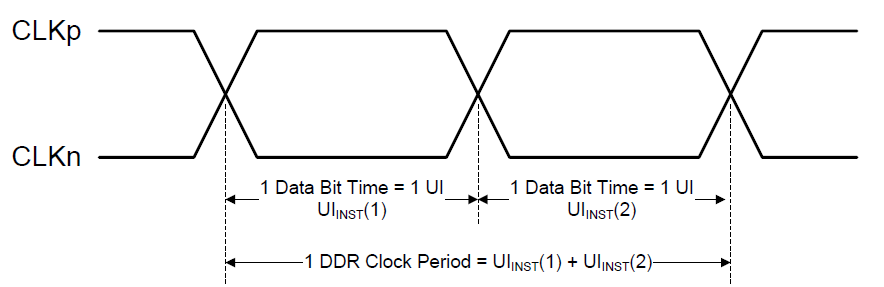

MIPI DPHY timing chart:

图3-16 Data lanes-Low Power Mode to/from High Speed Mode Timing

图3-17 Clock lanes- High Speed Mode to/from Low Power Mode Timing

Configure HS Timing Parameter:

-

HS_TRAIL/HS_EXIT /HS_PRPR/HS_ZERO/CLK_PRPR/CLK_ZERO/CLK_POST/CLK_TRAIL

Timing specification THS-PREPARE + THS-zero 145ns+10*UI THS-PREPARE 40ns+4*UI ~ 85ns +6*UI THS-ZERO >60ns+4*UI ~105ns+6*UI UI表示时间间隔,等于时钟通道上任何HS状态的持续时间.

UI的计算方法:

H_Total = HACT+HPW+HBP+HFP

V_Total = VACT+VPW+VBP+VFP

BitsPerPixel=24(RGB888)/18(RGB666)/16(RGB565)

Bitrate = (H_Total)*(V_Total)*FPS* BitsPerPixel/lane number

UI = 1/Bitrate

图3-18 DSI clock channel timing

如果Bitrate = 750Mps,UI = 1/Bitrate = 1.333ns,那么HS timing parameter计算结果为:

Timing specification Absolute time DA_HS_PREP value(Absolute time/(8*UI)) THS-PREPARE + THS-zero 145ns+10*UI > 158.33 ns > 15 THS-PREPARE 40ns+4*UI ~ 85ns +6*UI 45.32 ~ 92.98 ns 5 ~ 8 THS-zero >60ns+4*UI ~105ns+6*UI > 112.98~ 65.32 ns 10 ~ 7

Configure LP Timing Parameter:

-

CONT_DET/LPX/TA_GET/TA_SURE/TA_GO

low power parameters建议使用提供的默认值

4. 点屏配置¶

4.1. 配置DISP device¶

MI_S32 MI_DISP_SetPubAttr(MI_DISP_DEV DispDev, const MI_DISP_PubAttr_t *pstPubAttr)

-

配置DISP设备属性

参数 描述 DispDev DISP device ID pstPubAttr u32BgColor 背景色 eIntfType 接口类型(点屏使用E_MI_DISP_INTF_LCD) eIntfSync 输出timing(点屏使用E_MI_DISP_OUTPUT_USER) stSyncInfo u16Vact 等于屏参中u16Height u16Vbb 等于屏参中u16VSyncBackPorch u16Vfb 等于屏参中u16VTotal-(u16VSyncWidth+u16Height+u16VSyncBackPorch) u16Hact 等于屏参中u16Width u16Hbb 等于屏参中u16HSyncBackPorch u16Hfb 等于屏参中u16HTotal-(u16HSyncWidth+u16Width+u16HSyncBackPorch) u16Hpw 等于屏参中u16HSyncWidth u16Vpw 等于屏参中u16VSyncWidth u32FrameRate 等于屏参中u16DCLK*1000000/(u16HTotal*u16VTotal) 表中未列参数默认填0。

MI_S32 MI_DISP_Enable(MI_DISP_DEV DispDev) -

使能DISP设备

参数 描述 DispDev DISP device ID

4.2. 配置DISP video layer¶

MI_S32 MI_DISP_SetVideoLayerAttr(MI_DISP_LAYER DispLayer, const MI_DISP_VideoLayerAttr_t *pstLayerAttr)

-

设置DISP video layer属性

参数 描述 DispLayer DISP video layer ID pstLayerAttr stVidLayerDispWin u16X 0 u16Y 0 u16Width 等于屏参中u16Width u16Height 等于屏参中u16Height stVidLayerSize u16Width 等于屏参中u16Width u16Height 等于屏参中u16Height ePixFormat E_MI_SYS_PIXEL_FRAME_YUV_SEMIPLANAR_420 MI_S32 MI_DISP_EnableVideoLayer(MI_DISP_LAYER DispLayer) -

使能DISP video layer

参数 描述 DispLayer DISP video layer ID

4.3. 配置DISP input port¶

MI_S32 MI_DISP_SetInputPortAttr(MI_DISP_LAYER DispLayer, MI_DISP_INPUTPORT LayerInputPort, const MI_DISP_InputPortAttr_t *pstInputPortAttr)

-

设置DISP input port属性

参数 描述 DispLayer DISP video layer ID LayerInputPort DISP input port ID pstInputPortAttr stDispWin u16X Input port显示位置的x offset u16Y Input port显示位置的y offset u16Width Input port显示width(没有scaling,则等于u16SrcWidth) u16Height Input port显示height(没有scaling,则等于u16SrcHeight) u16SrcWidth Video source width u16SrcHeight Video source height MI_S32 MI_DISP_EnableInputPort(MI_DISP_LAYER DispLayer, MI_DISP_INPUTPORT LayerInputPort) -

使能DISP input port

参数 描述 DispLayer DISP video layer ID LayerInputPort DISP input port ID

4.4. 配置屏参¶

MI_S32 MI_PANEL_Init(MI_PANEL_LinkType_e eLinkType)

-

设置PANEL类型

参数 描述 eLinkType E_MI_PNL_LINK_TTL E_MI_PNL_LINK_MIPI_DSI MI_S32 MI_PANEL_SetPanelParam(MI_PANEL_ParamConfig_t *pstParamCfg) -

设置屏参

参数 描述 pstParamCfg pPanelName 屏的型号 u8Dither 1:enable Dither

0:disable DithereLinkType 接口类型

E_MI_PNL_LINK_TTL

E_MI_PNL_LINK_MIPI_DSIu8InvDCLK Pixel clk极性反转 u8InvDE DE极性反转 u8InvHSync Hsync极性反转 u8InvVSync Vsync极性反转 u16HSyncWidth 行同步信号脉宽 u16HSyncBackPorch 行同步信号后肩 u16VSyncWidth 场同步信号脉宽 u16VSyncBackPorch 场同步信号后肩 u16HStart u16HSyncWidth+16HSyncBackPorch u16VStart u16VSyncWidth+ u16VSyncBackPorch u16Width 行有效像素点数 u16Height 场有效行数 u16HTotal u16HSyncWidth+16HSyncBackPorch+HsyncFrontPorch u16VTotal u16VSyncWidth+ u16VSyncBackPorch+VsyncFrontPorch u16DCLK u16HTotal*u16VTotal*fps u16SpreadSpectrumStep 时钟延展幅度调制(详见展频计算表) u16SpreadSpectrumSpan 时钟延展频率调制(详见展频计算表) eOutputFormatBitMode 输出pixel format u8SwapOdd_RG Swap Channel R

0:default

1:select B

2:select G

3:select Ru8SwapEven_RG Swap Channel G

0:default

1:select B

2:select G

3:select Ru8SwapOdd_GB Swap Channel B

0:default

1:select B

2:select G

3:select Ru8SwapEven_GB Swap Rgb MSB/LSB

0:disable M/L swap

1:enable M/L swapeCh0 Chn0 lane selection(default:2)

0:select lane0

1:select lane1

2:select lane2

3:select lane3

4:select lane4

Selected lane将作为clk lane输出eCh1 Chn1 lane selection(default:4)

0:select lane0

1:select lane1

2:select lane2

3:select lane3

4:select lane4eCh2 Chn2 lane selection(default:3)

0:selec1t lane0

1:select lane1

2:select lane2

3:select lane3

4:select lane4eCh3 Chn3 lane selection(default:1)

0:select lane0

1:select lane1

2:select lane2

3:select lane3v4:select lane4eCh4 Chn4 lane selection(default:0)

0:select lane0

1:select lane1

2:select lane2

3:select lane3

4:select lane4表中未列参数默认填0

如果是MIPI panel,还需要对MIPI DSI进行配置,TTL panel只配置屏参即可。

MI_S32 MI_PANEL_SetMipiDsiConfig(MI_PANEL_MipiDsiConfig_t *pstMipiDsiCfg)参数 描述 pstMipiDsiCfg u8HsTrail Default: 0x05

60+4UI ~ MAXu8HsPrpr Default: 0x05

40+4UI ~ 85+6UIu8HsZero Default: 0x05

105+6UI ~ MAXu8ClkHsPrpr Default: 0x05

38ns ~ 95nsu8ClkHsExit Default: 0x05

100ns ~ maxu8ClkTrail Default: 0x05

60ns ~ maxu8ClkZero Default: 0x05

300ns-CLK_HS_PRPRu8ClkHsPost Default: 0x05

60+52UI ~ maxu8DaHsExit Default: 0x05

100ns ~ maxu8ContDet Default:0 u8Lpx Default:16 u8TaGet Default:26

5LPXu8TaSure Default:24

1LPX ~ 2LPXu8TaGo Default:50

4LPXu16Hactive Follow 屏参设定 u16Hpw u16Hbp u16Hfp u16Vactive u16Vpw u16Vbp u16Vfp u16Bllp 0 u16Fps Default:60 enLaneNum E_MI_PNL_MIPI_DSI_LANE_1

E_MI_PNL_MIPI_DSI_LANE_2

E_MI_PNL_MIPI_DSI_LANE_3

E_MI_PNL_MIPI_DSI_LANE_4enformat E_MI_PNL_MIPI_DSI_RGB565

E_MI_PNL_MIPI_DSI_RGB666

E_MI_PNL_MIPI_DSI_LOOSELY_RGB666

E_MI_PNL_MIPI_DSI_RGB888enCtrl E_MI_PNL_MIPI_DSI_CMD_MODE

E_MI_PNL_MIPI_DSI_SYNC_PULSE

E_MI_PNL_MIPI_DSI_SYNC_EVENT

E_MI_PNL_MIPI_DSI_BURST_MODEpu8CmdBuf Mipi panel初始化cmd buff指针

cmd buff格式:

cmd_buff[]=

{

Cmd, parameter cnt, parameter0, parameter1, … ,

Cmd, parameter cnt, parameter0, parameter1, … ,

Cmd, parameter cnt, parameter0, parameter1, … ,

………

}u32CmdBufSize Cmd buff size = sizeof(cmd_buff) u16DataClkSkew Date/clk 相位

范围:7-15u8PolCh0 Chn0极性

0:default

1:positive

2:negativeu8PolCh1 Chn1极性

0:default

1:positive

2:negativeu8PolCh2 Chn2极性

0:default

1:positive

2:negativeu8PolCh3 Chn3极性

0:default

1:positive

2:negativeu8PolCh4 Chn4极性

0:default

1:positive

2:negative

4.5. 初始化PANEL¶

一些panel需要cmd来初始化屏驱。MIPI panel的初始化cmd是通过MIPI data lane0来传输,cmd buff填写参考上节说明;TTL panel一般是通过SPI来发送cmd/parameters给屏驱,初始化需要的cmd要参考屏的数据手册,根据屏的初始化时序要求来下相应的初始化命令。

如果是采用SPI初始化的panel,SDK中有提供SPI发送数据的API。

MI_S32 MI_PANEL_GPIO_Init(MI_PANEL_GpioConfig_t *pstGpioCfg)

初始化panel复位、panel背光、panel enable以及SPI使用到的引脚。

| 参数 | 描述 | |

|---|---|---|

| pstGpioCfg | u16GpioBL | Panel背光 |

| u16GpioRST | Panel reset | |

| u16GpioSCL | SPI | |

| u16GpioSDO | ||

| u16GpioCS | ||

| u16GpioEN | Panel enable | |

MI_S32 MI_PANEL_SetGpioStatus(MI_U16 u16GpioNum, MI_BOOL bValue)

-

拉高/低某一个GPIO

参数 描述 u16GpioNum Gpio software num bValue 0:low

1:highMI_S32 MI_PANEL_SetCmd(MI_U32 u32Value, MI_U8 u8Bits) -

通过SPI发送数据

参数 描述 u32Value 需要发送的数据 u8Bits 该数据的长度(单位bit)

4.6. video显示¶

DISP/PANEL初始化完成,送需要显示的video data给DISP,一种方式是直接送YUV data到DISP,第二种方式是DISP绑定其他可以输出YUV data的模块,前提是可以输出YUV data的模块已经初始化完成,并且有数据输出。

第一种方式需要用到的相关API:

MI_S32 MI_SYS_ChnInputPortGetBuf (MI_SYS_ChnPort_t *pstChnPort,MI_SYS_BufConf_t *pstBufConf, MI_SYS_BufInfo_t *pstBufInfo, MI_SYS_BUF_HANDLE *pBufHandle, MI_S32 s32TimeOutMs) MI_S32 MI_SYS_ChnInputPortPutBuf (MI_SYS_BUF_HANDLE bufHandle, MI_SYS_BufInfo_t *pstBufInfo, MI_BOOL bDropBuf)

第二种方式需要用到的相关API:

MI_S32 MI_SYS_BindChnPort(MI_SYS_ChnPort_t *pstSrcChnPort, MI_SYS_ChnPort_t *pstDstChnPort,MI_U32 u32SrcFrmrate, MI_U32 u32DstFrmrate)

使用方法参考MI SYS API相关文档。

5. 参考DEMO¶

sdk/verify/feature/disp/disp_ut.c

使用方法:

-

编译

-

修改project/release/customer_tailor/nvr_default.mk,添加verify_disp:=enable

-

修改disp_ut.c,include对应的屏参头文件

-

cd sdk/verify/feature;

-

make disp_clean;make disp

-

cp disp/prog到执行目录

-

-

运行

./prog --interface lcd -l ttl -f ./YUV420SP_800_480.yuv -t yuv420 -n 1 -i 800_480 -c 0_0_800_480 -o 0_0_800_480

--interface //输出接口,点屏用lcd

-l //panel类型,ttl 或者 mipi

-f //文件路径

-t //pixel format

-n //chn num

-i //input size

-c //disp crop parameters

-o //disp show size

6. 调试方法和常见问题¶

6.1. 调试手段¶

-

procfs

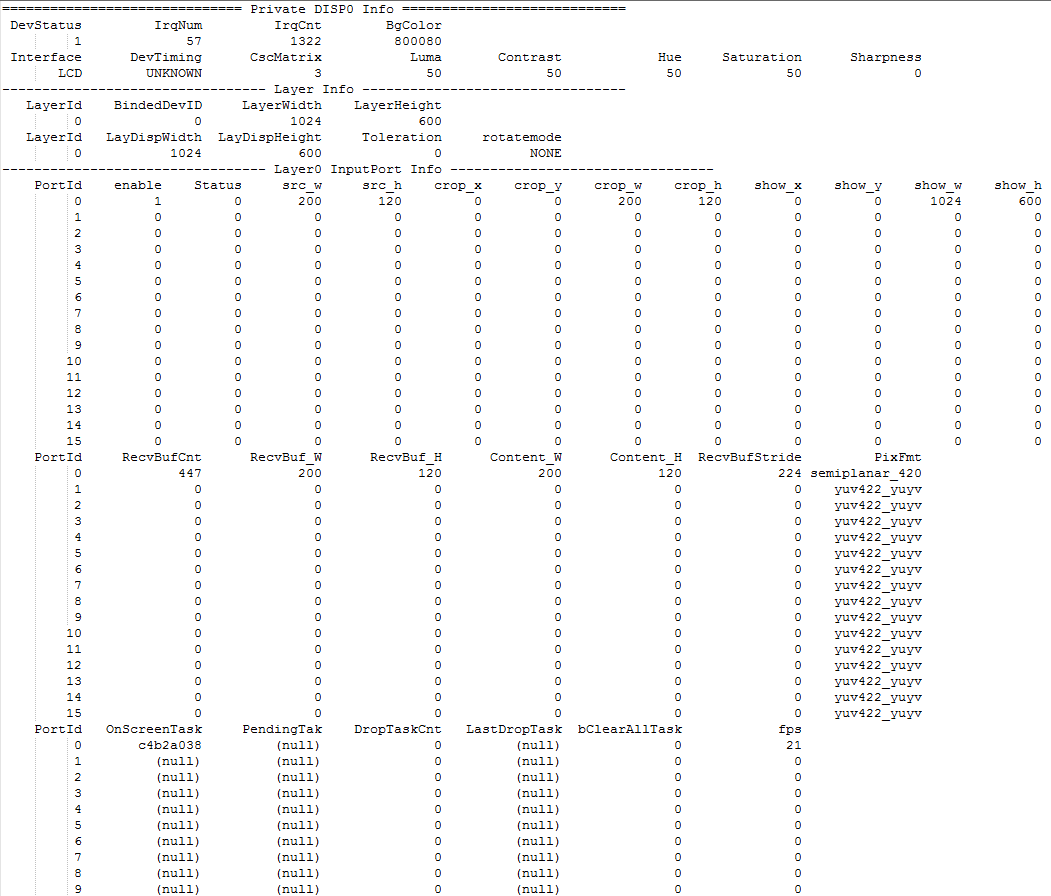

cat /proc/mi_modules/mi_disp/mi_disp0

图6-1

DISP procfs主要用来分析数据流是否正常,DISP相关设定是否合理和DISP工作状态。

-

数据流相关:

RecvBufCnt:分析DISP是否拿到input buff

RecvBuf_W:input buff width

RecvBuf_H:input buff height

Content_W:input buff有效width

Content_H:input buff有效height

RecvBufStride:input buff stride

PixFmt:input buff pixel format

-

功能性设定:

crop_x/crop_y/crop_w/crop_h: input port crop parameters

show_x/show_y/show_w/show_h: display input port show size

rotatemode: rotate mode

CscMatrix/Luma/Contrast/Hue/Saturation/Sharpness: PQ

-

状态相关:

DevStatus:DISP device使能状态

IrqCnt:DISP硬件中断次数

enable:DISP input port使能状态

DISP没有正常显示的情况下,首先检查以上三个部分是否正常。

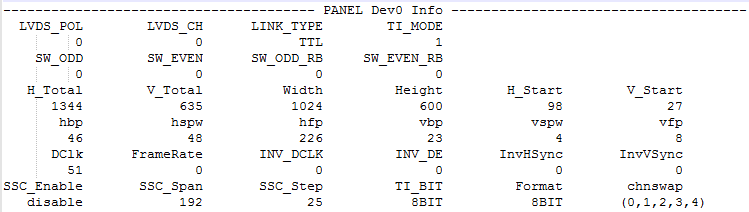

cat /proc/mi_modules/mi_panel/mi_panel0

图6-2

PANEL procfs主要用来分析屏参设定是否生效。

-

-

register

跟显示相关需要关注的寄存器:

bank Addr Description 101e 0d [bit8-bit11] TTL mode

0001: SSR201/202

1100: SSR623

[bit12-bit13] MIPI TX mode

01: 4 lane1038 54 [bit0-bit3] clk_mop

[bit0] disable clk

[bit1] inv clk

[bit2-bit3] select clk source

00:320Mhz

01:384Mhz

10:288Mhz

11:clk_miu53 [bit0-bit3] clk_disp_432

[bit0] disable clk

[bit1] inv clk

[bit2-bit3] select clk source

00: 432Mhz

[bit8-bit11] clk_disp_216

[bit8] disable clk

[bit9] inv clk

[bit10-bit11] select clk source

00: 216Mhz

01: 108Mhz63 [bit0-bit5] clk_sc_pixel

[bit0] disable clk

[bit1] inv clk

[bit2-bit5] select clk source

0000:240Mhz

0001:216Mhz

0010:192Mhz

0011:172Mhz

0100:144Mhz

0101:123Mhz

0110:108Mhz

0111:86Mhz

1000:72Mhz

1001:54Mhz

1010:lpll_clk6f [bit0-bit4] clk_mipi_tx_dsi

[bit0] disable clk

[bit1] inv clk

[bit2-bit4] select clk source

000:lpll_clk

001:160Mhz

010:144Mhz

011:108Mhz

100:216Mhz

101:240Mhz1128 07 [bit0-bit3] pattern gen

[bit0] select source of mace

0: from scaling patgen

1: from external video source

[bit1-bit3] select pattern mode

000: 1-pix gray ramp

001: 16-pix gray ramp

010: 32-pix gray ramp

011: 64-pix gray ramp

100: 16-pix gray stick

101: 16-pix colorbar

110: 32-pix colorbar

111: 64-pix colorbar1129 11 [bit0-bit12] h total 12 [bit0-bit12] v total 13 [bit0-bit12] hsync start 14 [bit0-bit12] hsync end 15 [bit0-bit12] vsync start 16 [bit0-bit12] vsync end 17 [bit0-bit12] H frame de start 18 [bit0-bit12] H frame de end 19 [bit0-bit12] V frame de start 1a [bit0-bit12] V frame de end 1b [bit0-bit15] no signal color

[bit0-bit4] B channel

[bit5-bit9] G channel

[bit10-bit14] R channel

[bit15] Forced to show no signal color7e [bit0-bit5] rgb swap

[bit0-bit1] swap for B channel

[bit2-bit3] swap for G channel

[bit4-bit5] swap for R channel

[bit6-bit7] rgb mode

00:rgb 888

01:rgb 666

10:rgb 565-1

11:rgb 565-2

[bit8] MSB/LSB swap1406 00 [bit0] Gwin0 enable 10 [bit0] Gwin1 enable 20 [bit0] Gwin2 enable 30 [bit0] Gwin3 enable 40 [bit0] Gwin4 enable 50 [bit0] Gwin5 enable 60 [bit0] Gwin6 enable 70 [bit0] Gwin7 enable 1407 00 [bit0] Gwin8 enable 10 [bit0] Gwin9 enable 20 [bit0] Gwin10 enable 30 [bit0] Gwin11 enable 40 [bit0] Gwin12 enable 50 [bit0] Gwin13 enable 60 [bit0] Gwin14 enable 70 [bit0] Gwin15 enable 1033 4e [bit0-bit15] ssc

[bit0-bit11] step

[bit15] enable ssc4f [bit0-bit13] ssc span

6.2. 常见问题¶

-

背光可以亮,但是没有画面

请排查如下问题:

-

检查屏参是否满足panel spec要求

-

数据流是否正常,是否有input buff输入

-

DISP device/layer/input port相关设定是否合理

-

panel init是否成功,需要SPI初始化的TTL panel可以量测SPI信号是否正常,initial cmd是否有正确传输

-

检查Hsync/Vsync/DE/Dclk极性是否满足panel spec

-

MIPI panel检查clk lane/data lane线序和软件设定是否一致

-

查看register BK101e addr 0d 是否有切对TTL mode/MIPI mode

-

检查clk相关register是否都有打开

-

MOP gwin是否有打开

-

pattern gen是否可以正常输出

-

-

分屏现象

图6-3

如果是H方向,尝试加大Hsync Front porch和Htotal,Hsync和Hsync back porch保持不变

如果是V方向,尝试加大Vsync Front porch和Vtotal,Vsync和Vsync back porch保持不变

-

色偏

图6-4 色偏

图6-5 正常

-

检查R/G/B单色是否输出正常,如果是TTL panel,可以关掉3x3 matrix(BK1129_30 bit0=0,BK1129_3c bit0=0),利用BK1129_1b输出RGB单色并量测R/G/B channel每根是否都有正常输出。

-

调整VBP,VPW/VFP维持不变

-

检查是否需要做R/G/B channel swap或者RGB M/L swap。

-

7. TTL/MIPI硬件连接¶

-

如下所示,芯片TTL输出默认硬件连接顺序

Pin Number PADName reg_ttl_mode 1 28pin Default Pin56 PAD_TTL0 TTL_DOUT[0] R0 G0 B0 R7/G7/B7 Pin57 PAD_TTL1 TTL_DOUT[1] R1 G1 B1 R6/G6/B6 Pin58 PAD_TTL2 TTL_DOUT[2] R2 G2 B2 R5/G5/B5 Pin59 PAD_TTL3 TTL_DOUT[3] R3 G3 B3 R4/G4/B4 Pin60 PAD_TTL4 TTL_DOUT[4] R4 G4 B4 R3/G3/B3 Pin61 PAD_TTL5 TTL_DOUT[5] R5 G5 B5 R2/G2/B2 Pin65 PAD_TTL6 TTL_DOUT[6] R6 G6 B6 R1/G1/B1 Pin66 PAD_TTL7 TTL_DOUT[7] R7 G7 B7 R0/G0/B0 Pin67 PAD_TTL8 TTL_DOUT[8] G0 B0 R0 Pin68 PAD_TTL9 TTL_DOUT[9] G1 B1 R1 Pin69 PAD_TTL10 TTL_DOUT[10] G2 B2 R2 Pin70 PAD_TTL11 TTL_DOUT[11] G3 B3 R3 Pin71 PAD_TTL12 TTL_DOUT[12] G4 B4 R4 Pin72 PAD_TTL13 TTL_DOUT[13] G5 B5 R5 Pin73 PAD_TTL14 TTL_DOUT[14] G6 B6 R6 Pin74 PAD_TTL15 TTL_DOUT[15] G7 B7 R7 Pin79 PAD_TTL16 TTL_DOUT[16] B0 R0 G0 Pin80 PAD_TTL17 TTL_DOUT[17] B1 R1 G1 Pin81 PAD_TTL18 TTL_DOUT[18] B2 R2 G2 Pin82 PAD_TTL19 TTL_DOUT[19] B3 R3 G3 Pin83 PAD_TTL20 TTL_DOUT[20] B4 R4 G4 Pin84 PAD_TTL21 TTL_DOUT[21] B5 R5 G5 Pin85 PAD_TTL22 TTL_DOUT[22] B6 R6 G6 Pin86 PAD_TTL23 TTL_DOUT[23] B7 R7 G7 Pin87 PAD_TTL24 TTL_CK Pin88 PAD_TTL25 TTL_HSYNC Pin89 PAD_TTL26 TTL_VSYNC Pin90 PAD_TTL27 TTL_DE -

如下表所示,芯片默认MIPI硬件连接顺序。

Pin Location Ball Pin Name Function Pin65 PAD_TTL6 MIPI_TX_P_CH0 Pin66 PAD_TTL7 MIPI_TX_N_CH0 Pin67 PAD_TTL8 MIPI_TX_P_CH1 Pin68 PAD_TTL9 MIPI_TX_N_CH1 Pin69 PAD_TTL10 MIPI_TX_P_CH2 Pin70 PAD_TTL11 MIPI_TX_N_CH2 Pin71 PAD_TTL12 MIPI_TX_P_CH3 Pin72 PAD_TTL13 MIPI_TX_N_CH3 Pin73 PAD_TTL14 MIPI_TX_P_CH4 Pin74 PAD_TTL15 MIPI_TX_N_CH4