MISC Q&A

Q1: 如何在SSD210上支持SPI panel?

在demo board上硬件相关padmux如下:

需要针对HW做如下更改:

-

kernel DTS (kernel/arch/arm/boot/dts/pioneer3-ssc021a-s01a-demo-padmux.dtsi)做添加如下更改:

<PAD_TTL0 PINMUX_FOR_SPI1_MODE_3 MDRV_PUSE_SPI1_CZ>, <PAD_TTL1 PINMUX_FOR_SPI1_MODE_3 MDRV_PUSE_SPI1_CK>, <PAD_TTL2 PINMUX_FOR_SPI1_MODE_3 MDRV_PUSE_SPI1_DI>,

-

测试demo(smartdisp_demo / P3_ReleaseDemo/panel/SpiPanel/)需要做如下更改:

src/spi_operation.c static const char *device = "/dev/spidev1.0"; src/spi_panel.c #define RS_GPIO_PIN (20) #define RST_GPIO_PIN (21) #define BL_GPIO_PIN (5) //Backlight 没有更改,因为SSD210 demo board不需要控制这个

Q2: 母片制作时,SPINAND.INI里面的nandid填的不是实际的flash id,为什么母片烧录后还可以正常起来?

在制作母片时,会根据nandid到cis的flashlist里面找是否支持这颗flash,如果有对应的ID就会按照填的nandid对应的flash参数去初始化。

如果两颗flash下面的参数差异不大,也是可以正常起来的。但是建议nandid还是要按实际的flash id填写,避免不必要的风险!

Q3: 如何动态调节cpu频率?

方法1:在kernel dts里面位置: kernel\arch\arm\boot\dts\pioneer3.dtsi放开需要开启的cpu频率(如果需要固定某一个频率,则只需放开对应的一个频率即可):

方法2:在板子的shell终端按如下方法配置(板子直接配置频率的前提是dts里面有打开对应的选项,这个方法只能临时生效,仅做debug使用。):

echo 1000000 > /sys/devices/system/cpu/cpufreq/policy0/scaling_max_freq echo 1000000 > /sys/devices/system/cpu/cpufreq/policy0/scaling_min_freq

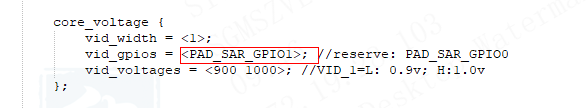

注意:cpu频率改变了,对应的core电压也要对应调整,目前驱动是通过在kernel\arch\arm\boot\dts\pioneer3.dtsi中设定要调节core电压的gpio,需要确保这根pin没有做其他用途。

Q4: 使用7*7的keypad配置,但是实际只接了6*7的pin,多出来的pin可以做其他用途吗?

多出来的pin是可以做其他用途的。具体keypad pin对应key的映射关系如下:

如果接的是6*7,对应的read6这根pin是可以做其他用途的,对应下图的就是PAD_KEY0。

其他4*4,3*3的组合对应mapping关系也是如此。

Q5: PSPI跟SPI有什么差异?PSPI接panel和sensor差异在哪里?

PSPI是SStar做的一个私有的spi协议,支持master/slave 模式,最大CLK支持216Mhz。

注意:作为master因为要二分频,所以最大clk为216/2=108Mhz;作为slave接收的clk要为发送的4倍,即能接收的最大pclk为216/4=54Mhz。

接panel的线序如下:

目前是用TE来控制同步时序,MCU这边做好一张图后等panel发送te信号再发送。设定的CLK需要满足>= panel htotal * panel vtotal *fps

接sensor的线序如下:

因为目前默认接的就是sensor,所以sensor cs接地就可以了,MCU可以省掉cs pin。需要注意的是sensor发送的clk必须小于54M,同时我们发送给sensor的mclk也必须在sensor的接收范围内。

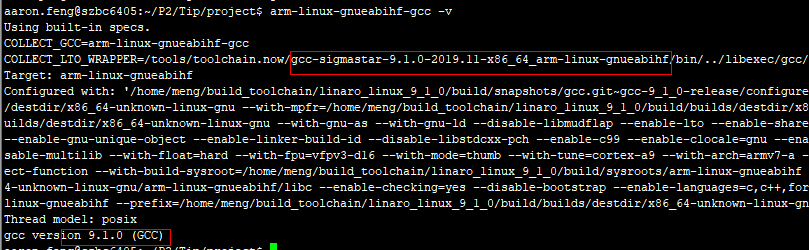

Q6: 如何确定toolchain对应gcc & libc & binutils的版本?

gcc版本:

libc版本:

project\release\dispcam\p3\common\glibc\9.1.0\package\libc-2.30.tar.gz

binutils版本:

ToolChain源码获取:https://git.linaro.org/toolchain

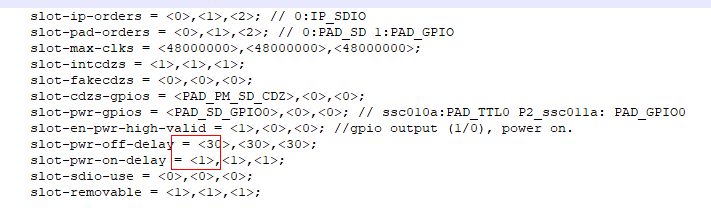

Q7: SDIO wifi reboot开机时是否需要做rst?目前是如何实现的?

目前接SDIO wifi有两种供电方式:

-

长供电,reboot靠拉rst pin来复位wifi模块

-

通过sdio的power pin供电,reboot时sdio驱动内部拉power pin来复位wifi模块

不管哪种方式reboot都需要复位wifi模块,对于主控端power和rst pin都是用的PAD_SD_GPIO0。长供电的case,PAD_SD_GPIO0接到wifi模块的rst pin;

通过sdio power pin供电的case,PAD_SD_GPIO0是接到wifi模块的powerpin。通过设定如下dts中的power on/power off delay来控制rst 拉低和拉高后多久做wifi init的时间(单位:ms)

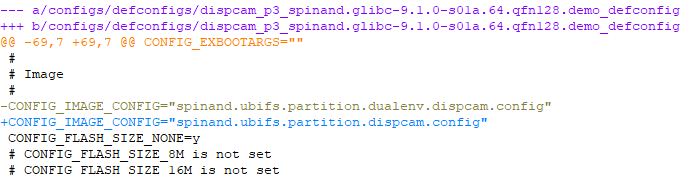

Q8: 如何新增ubi分区?

新增方法如下:

-

选择使用的分区配置文件

-

创建挂载的分区目录以及要放入的文件,以把project/board/test/test文件放入板子根目录test为例

-

增加新增分区配置信息

Q9: 如何固定cpu电压?固定电压之后,能否把动态调整core电压的Pin脚做gpio使用?

动态调整core电压的Pin脚可做gpio使用。

case 1:固定频率 1G,需要注意以下三点:

-

kernel\arch\arm\boot\dts\pioneer3.dtsi中固定cpu频率,比如固定到1Ghz:

-

kernel config关闭CONFIG_SS_VOLTAGE_CTRL后,就不会再去控制core这根pin;

-

硬件动态调整core电压的Pin脚已经断开,不控制电压,电压硬件要固定好,实际测量看是否符合设定:CPU 1G -> 1.0V(从上电到IPL/UBOOT/KERNEL一直维持在1V)

case 2:固定频率 800M,需要注意以下三点:

-

kernel\arch\arm\boot\dts\pioneer3.dtsi中固定cpu频率,比如固定到800M:

-

kernel config关闭CONFIG_SS_VOLTAGE_CTRL后,就不会再去控制core这根pin;

-

硬件动态调整core电压的Pin脚已经断开,不控制电压,电压硬件要固定好,实际测量看是否符合设定:CPU 800MHz -> 0.9V(从上电到IPL/UBOOT/KERNEL一直维持在 0.9V)

case 3:动态频率1G/800M,根据需要动态调整,需要注意以下三点:

-

kernel\arch\arm\boot\dts\pioneer3.dtsi中固定cpu频率,比如固定到800M;

-

kernel config打开CONFIG_SS_VOLTAGE_CTRL后,就会去控制core这根pin;

-

硬件动态调整core电压的Pin脚已经连接相关电路,控制电压,实际测量看是否符合设定:CPU 1G -> 1.0V(从上电到IPL/UBOOT一直维持在1V)

-

CPU 800MHz -> 0.9V or CPU 1G -> 1.0V(KERNEL根据相关情况控制是否在1G或800M 1V/0.9V)

cpu的频率可以通过cat /sys/devices/system/cpu/cpufreq/policy0/cpuinfo_cur_freq来查看当前的cpu频率。

拉高cpu loading,请使用拉高CPU loading:

...