Network Q&A

Q1: How to use mac and phy on SigmaStar platform?

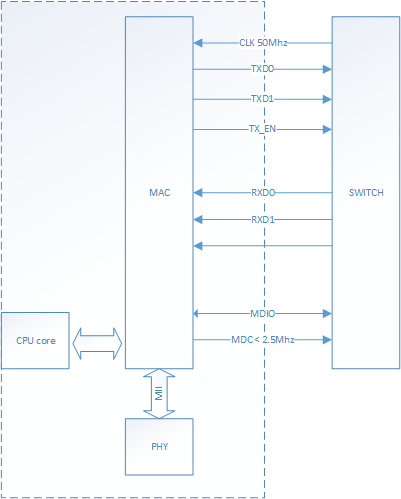

Ethernet is composed of CPU, MAC and PHY. MAC is at the link layer; PHY is at the physical layer and is connected to RJ45.

SigmaStar platform reserves RMII interface of the MAC for users to choose whether to connect an external switch. If not, the MAC and PHY are integrated in the internal Ethernet of the chip by default; if it is, switch the pin to the Ethernet of the rmii.

The structure diagram is as follows:

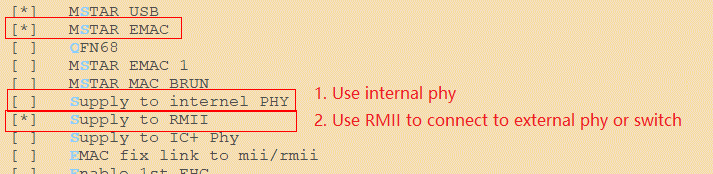

Switch to rmii mode in padmux:

//for eth0 rmii <PAD_GPIO0 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_MDIO>, <PAD_GPIO1 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_MDC>, <PAD_GPIO2 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_COL>, <PAD_GPIO3 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_RXD0>, <PAD_GPIO4 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_RXD1>, <PAD_GPIO5 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_TX_CLK>, <PAD_GPIO6 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_TXD0>, <PAD_GPIO7 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_TXD1>, <PAD_GPIO8 PINMUX_FOR_ETH0_MODE_11 MDRV_PUSE_ETH_TX_EN>,

Q2: How to confirm that the data sent by MDIO & MDC is normal through the external switch of RMII?

MDIO is mainly used in uboot and kernel to send initialization data to switch. The confirmation method is as follows:

uboot:

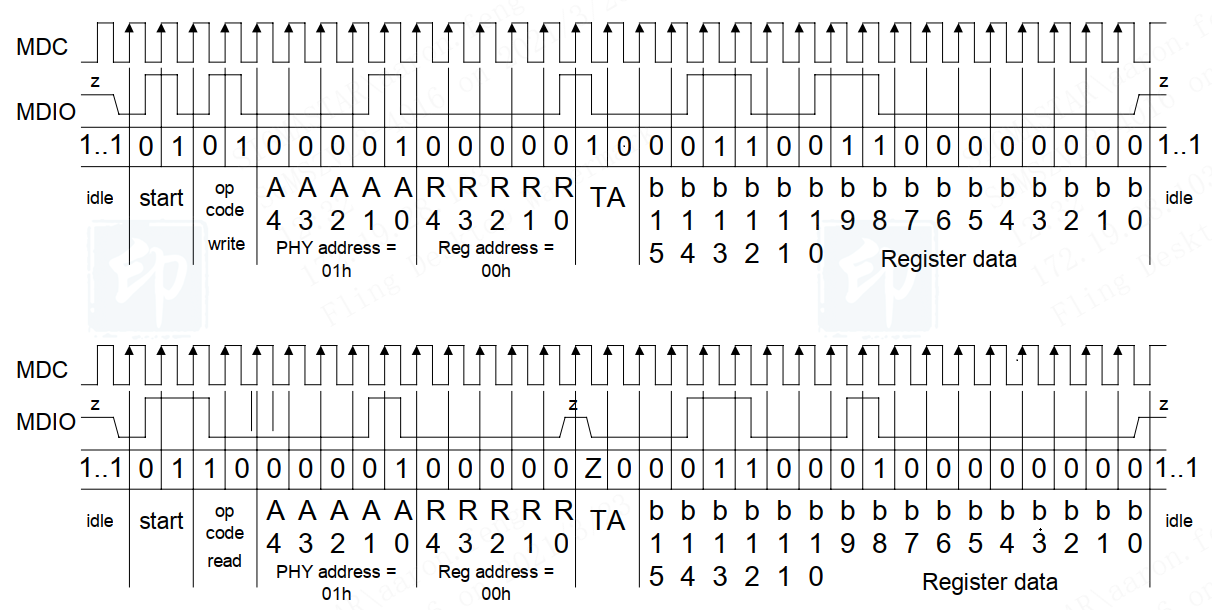

The following is the corresponding API for reading and writing, and the waveform diagram.

read:

void MHal_EMAC_read_phy(unsigned char phy_addr, unsigned char address,u32 *value)

write:

void MHal_EMAC_write_phy (unsigned char phy_addr, unsigned char address, u32 value)

Note: When reading, the master will become sampling at the falling edge after the TA signal.

Sampling on the rising edge all the time during write.

Q3: How to enable RMII interface in uboot?

The chip has only one MAC peripheral, which is configured in menuconfig.

> Device Drivers > MStar drivers

-

Use RMII to connect the external phy chip IP101G.

Software implementation process:

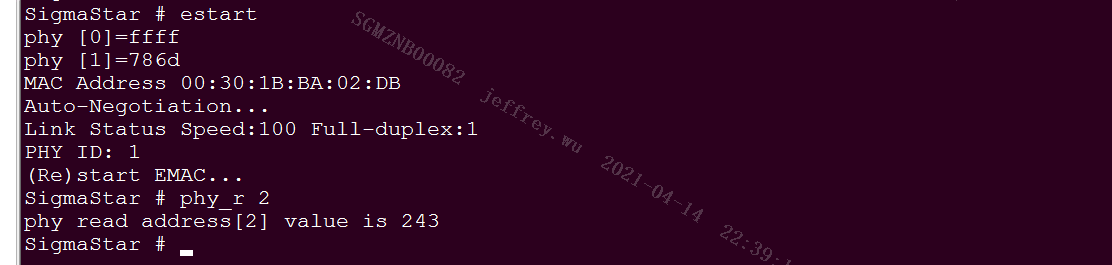

Run estart under uboot to initialize mac, but it is actually implemented by calling MDrv_EMAC_initialize. The reference code is in boot/drivers/mstar/emac/cmd_emac.c.

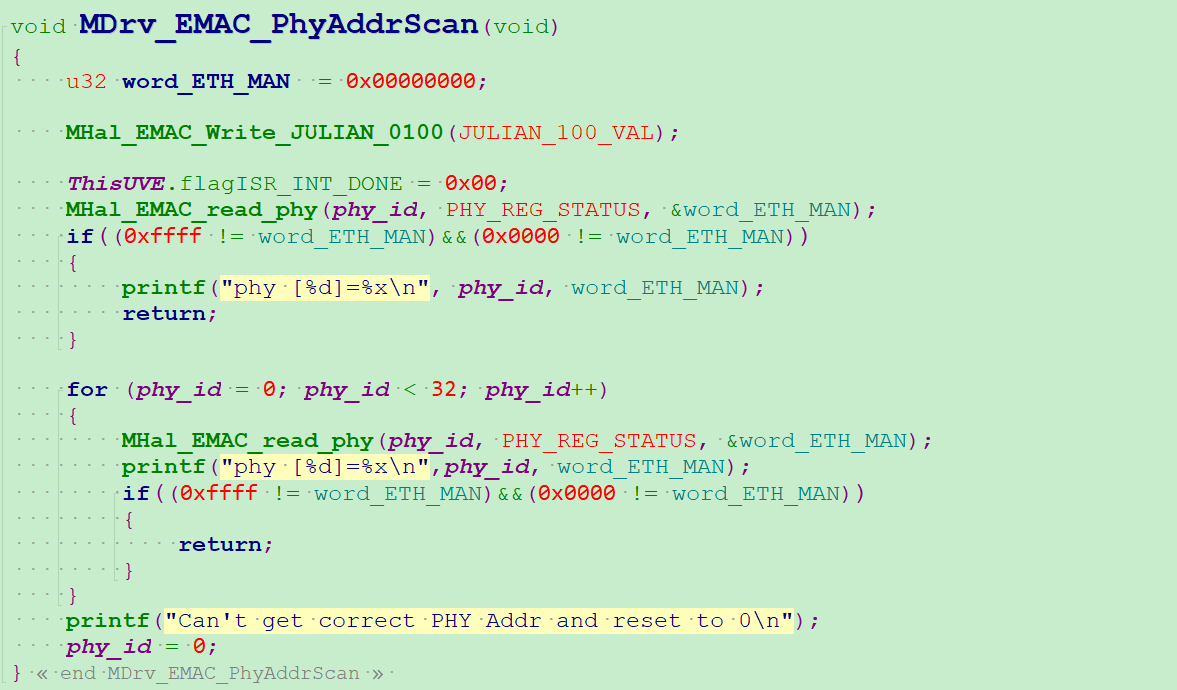

Call MDrv_EMAC_PhyAddrScan in MDrv_EMAC_initialize to find the external phy chip. The reference code is in boot drivers/mstar/emac/mdrv_emac.c.

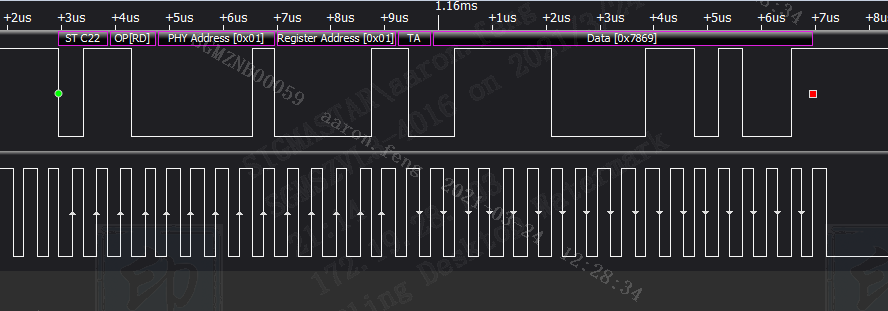

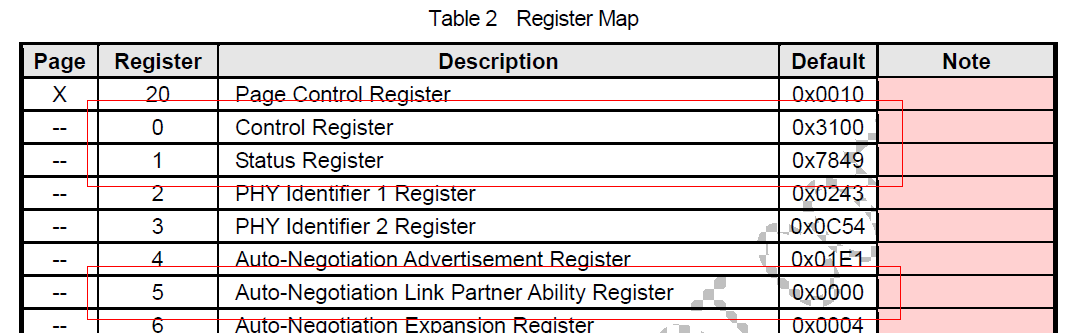

MHal_EMAC_read_phy reads the value of the phy register by MDIO. Checking the data sheet of the chip IP101G shows that PHY_REG_STATUS is register 1.

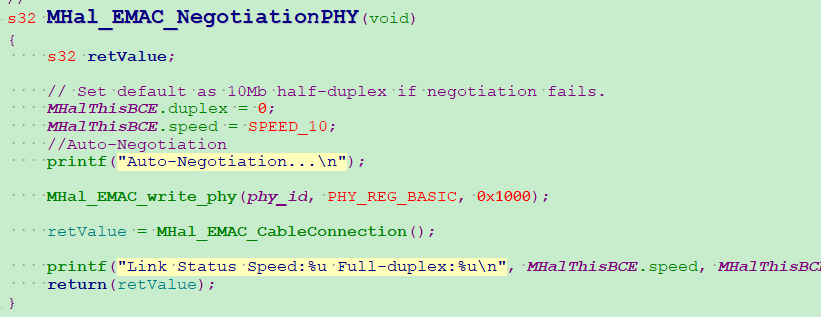

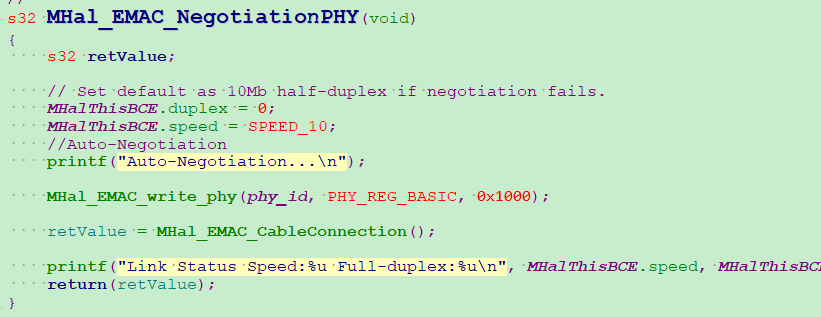

After finding the phy, call MDrv_EMAC_HW_init → MHal_EMAC_NegotiationPHY → MHal_EMAC_CableConnection, IP101G Auto-Negotiation will be configured in MHal_EMAC_NegotiationPHY, and MHal_EMAC_CableConnection will try to connect to IP101G.

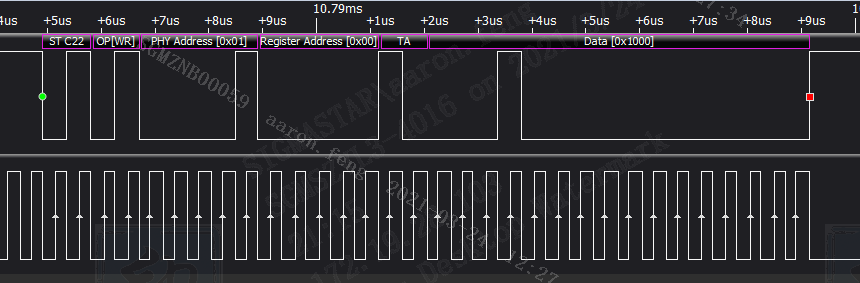

MHal_EMAC_write_phy writes the value of the phy register through MIDO. Checking the IP101G data sheet shows that PHY_REG_BASIC is register 0, and PHY_REG_LINK_PARTNER is register 5.

MHal_EMAC_write_phy writes the value of the phy register through MIDO. Checking the IP101G data sheet shows that PHY_REG_BASIC is register 0, and PHY_REG_LINK_PARTNER is register 5. -

After mac initialization is completed, use the phy_r and phy_w commands to test whether the phy is successfully connected.

Use phy_r to read the value of IP101G register 2, which is a read-only register and the value is always 0x0243.

-

As described above, to connect other types of phy chips or switch chips, use MHal_EMAC_write_phy and MHal_EMAC_read_phy to configure the registers.

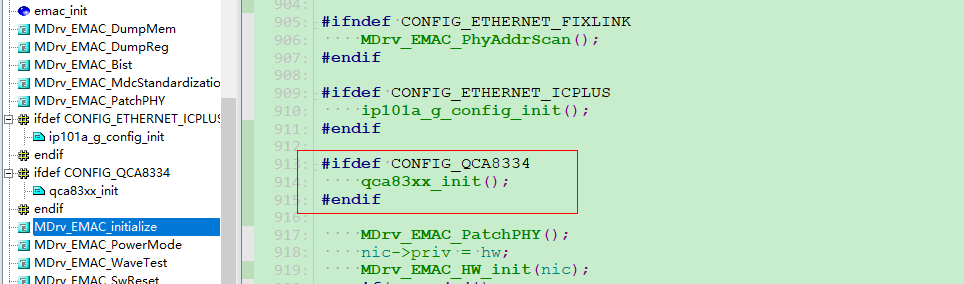

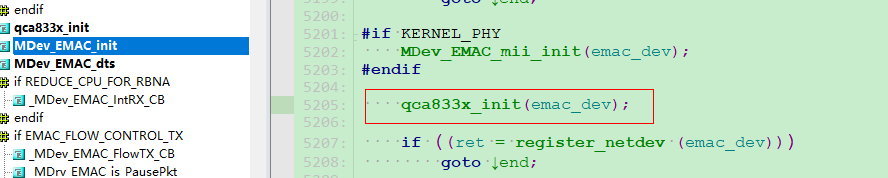

Add QCA833X series switch chip:

Create a new initialization function qca83xx_init to configure the chip's registers, and then place this function in MDrv_EMAC_initialize.

-

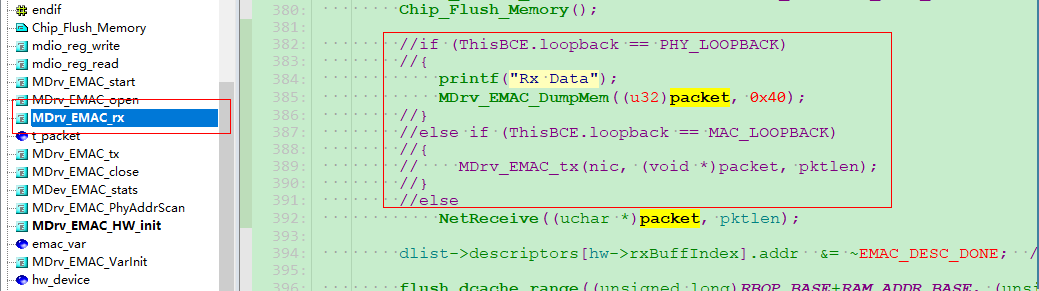

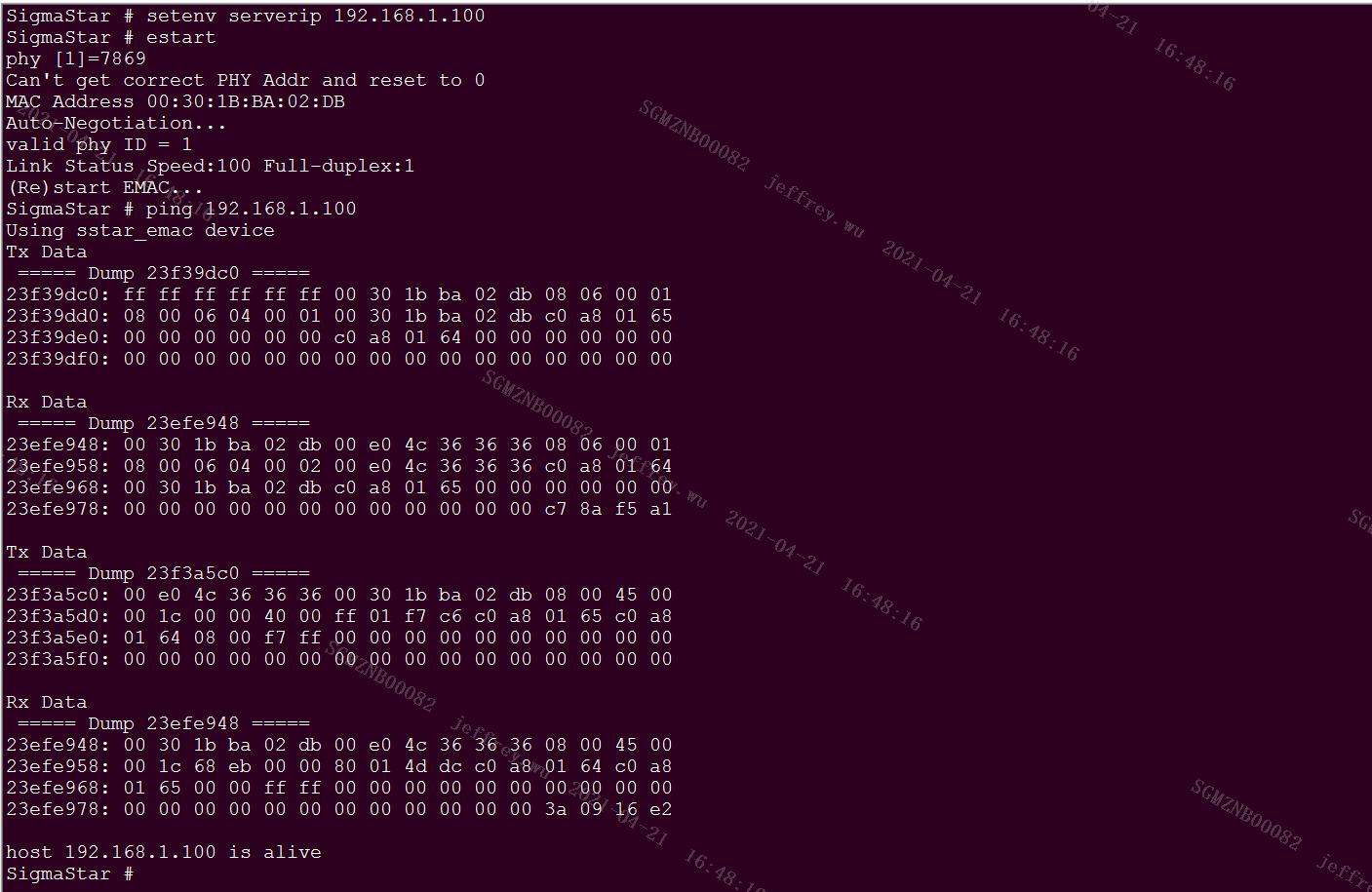

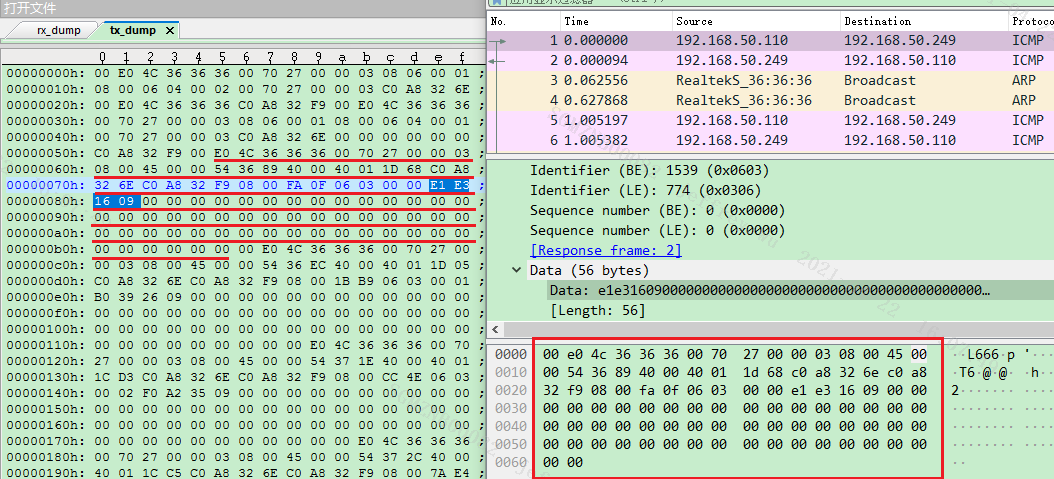

Use MDrv_EMAC_DumpMem to dump the sent and received data and test the phy communication.

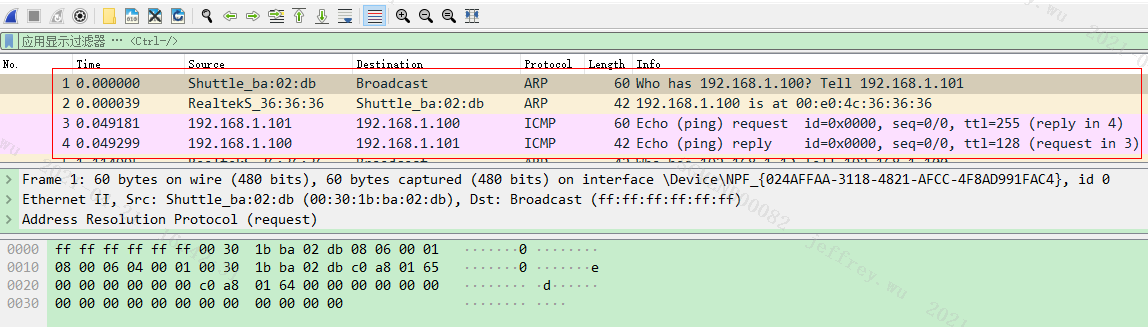

Modify MDrv_EMAC_rx and MDrv_EMAC_tx as follows. After setting ipaddr and serverip in uboot, use the ping command to test the network. PC uses the wireshark software to capture packets. If the packets sent by uboot are consistent with PC, the communication is normal.

Compare the dumped data in uboot with the data captured by wireshark.

Q4: How to use RMII in kernel?

-

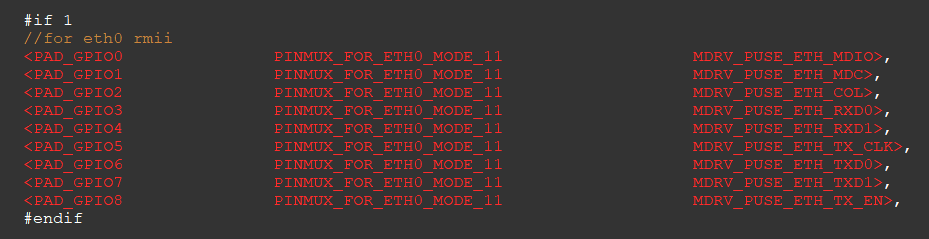

Configure RMII pin padmux

Open

kernel/arch/arm/boot/dts/pioneer3-ssc020a-s01a-demo-padmux.dtsiand configure RMII as follows.

-

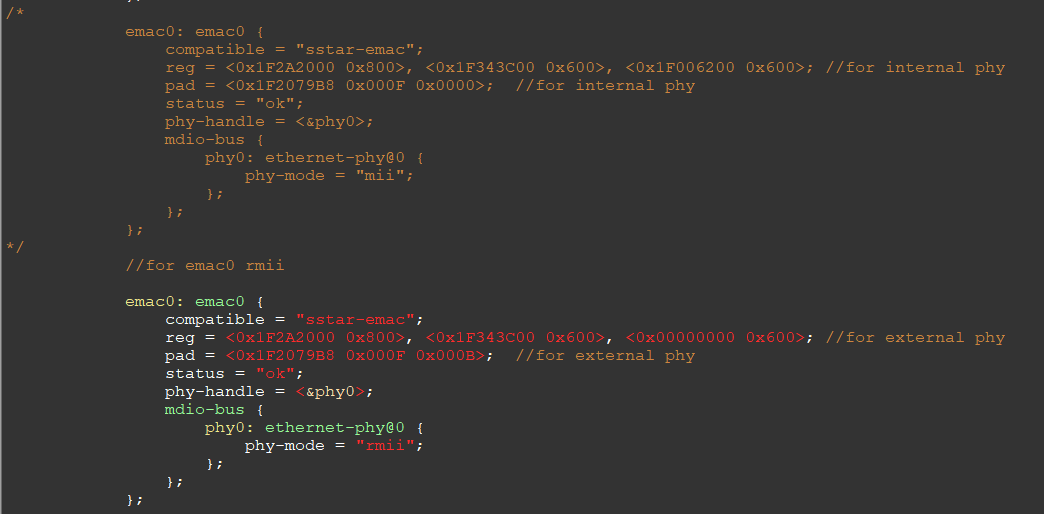

Modify dts tree to enable RMII

Open

kernel/arch/arm/boot/dts/pioneer3-ssc020a-s01a-demo.dtsand switch phy-mode to RMII.

-

Add initialization code, configure external phy or switch

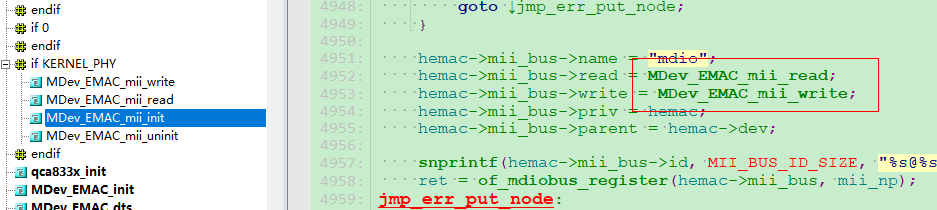

There is no need to modify the code when adding an external phy. If you add a switch or need to configure the chip register through mdio, you can modify the code as follows.

Open

kernel/drivers/sstar/emac/mdrv_emac.cto find MDev_EMAC_init, and add initialization code after it. As follows, create a new qca833x_init and call mdio write/read to configure the external phy/switch register.MDev_EMAC_mii_read(struct mii_bus *bus, int phy_addr, int phy_reg); //MDIO read register MDev_EMAC_mii_write(struct mii_bus *bus, int phy_addr, int phy_reg, u16 val); //MDIO write register

-

phy/switch communication test

If the network is not connected, you can test the phy/switch communication as follows.

MDIO test:

After kernel is running, use the following commands to read or write phy register.

echo phy_r phyAddress > /sys/devices/virtual/mstar/emac0/phyStatusWR echo phy_w phyAddress phyValue > /sys/devices/virtual/mstar/emac0/phyStatusWR

RMII test:

The tx_dump/rx_dump provided in the emac driver can save the data sent by RMII to file. Open

#define PACKET_DUMPinkernel/drivers/sstar/emac/mdrv_emac.c; open#define CONFIG_MSYS_KFILE_APIinkernel/drivers/sstar/msys/ms_msys.c, and recompile the kernelAfter the kernel is running, use the following command to open tx_dump/rx_dump, tx_dump and rx_dump will be generated in the /tmp directory.

echo 1 > /sys/devices/virtual/mstar/emac0/tx_dump echo 1 > /sys/devices/virtual/mstar/emac0/rx_dump

Set the ip and mac address of the board, use the ping command to connect to PC, the driver code will save the data sent and received by RMII in tx_dump and rx_dump files. At the same time, PC opens wireshark to capture the network packet, and compares it with the data in tx_dump and rx_dump.

...