isp fifo full异常打印问题案例

1. ISP FIFO FULL 问题¶

ISP P0 FIFO FULL(13)(0) 13 input line cnt 0 isp dma line cnt

下一帧数据来了, 但是上一帧还没有做完,发生fifo full。 fifo full发生后,软件会reset isp IP。reset 原因是,fifo full 一旦发生就会一直回档, 可以通过reset IP, 尝试是否可以救回来。

2. 常见参数原因¶

2.1. 确认HDR Type 是否正确¶

im415/SCXXX VC

Imx307/274 DoL

2.2. VIF->VPE realtime下做了scaling up¶

在realtime mode下,scl 的处理速度要比Isp更快, scaling up 会导致scl处理时间更长,导致isp 比scl 快, 这样scl 就会回档前端。

2.3. scl clk 没有设置¶

cat /sys/class/mstar/mscl/clk

cat /sys/class/mstar/mscl/clk 确认scl clk 是否有设置,默认345M ,code 在hal_scl.c HalSclHwGetDefaultFclk1Clock

3. 底层原因¶

3.1. BW不够¶

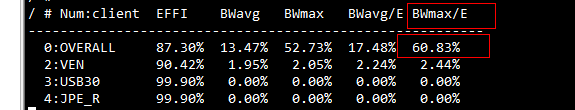

抓取BW 数据

echo 1000 > /sys/devices/system/miu/miu0/monitor_set_duration_ms //通常取1秒的平均值 echo all > /sys/devices/system/miu/miu0/monitor_client_enable cat /sys/devices/system/miu/miu0/measure_all

注意:不要在狂刷isp fifo full 打印时去抓BW, 因为isp fifo full 打印太多,帧率一定已经掉下来, 那后端IP 的BW 一定已经很低了,这时候BW没有参考价值。 可以通过尝试降低sensor 帧率或者主码流分辨率, 来找到一个临界点FIFO FULL 没有那么多,来抓BW。

判断BW 是否紧张,通过看all 的Bwmax 峰值, 如果已经到90%, 说明已经超规格了。请系统的owner 看下BW数据是否有异常, 是否可以调整IP 访问MIU 优先级,降低BW。

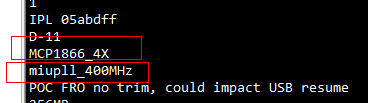

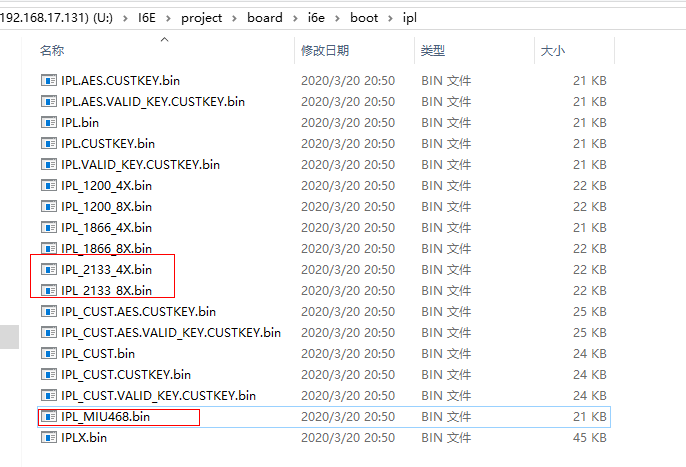

另外可以尝试替换IPL 到更高的clock,可以从1866替换成2133,但要确认所用的DDR 是否支持到这个频率。

但是上面提高clk 或者2133 会导致功耗更高。

3.2. 后端回档¶

能够造成回档的两个模块之间一定是realtime。首先要理清楚链路上有哪些realtime 模块。通常有 VIF->ISP->SCL->GOP->JPEG, 在发生FIFO FULL时,将一级一级的模块拿掉,判断哪一级回档。

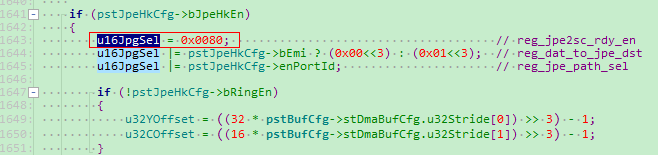

0x1302 0x16 bit0 handshaking ack tie enable

0: isp 吐数据scl

1: isp 断开与scl 连接。

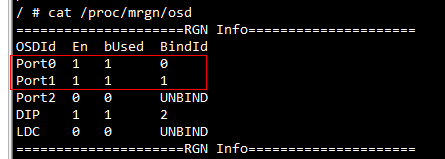

确定scl 上bind 的是哪几个GOP

0x121a 0x60 bit0 osd0 0x64 bit0 osd1 0x68 bit0 osd2

关掉对应的Osd hal_scl.c _HalSclDmaSetJpeHandShakeConfig()

改成0,目前每一张frame 都会写reg,所以riu改没有用(在给mhal提需求提供debug 方法)。

对应reg 0x1218 0x64 bit7,Jpeg to Sc ready control, 设置为0, SC 不看Jpeg 回档。

理清哪个模块造成回档, 然后抓出对应模块reg或者info 提供给owner debug。

isp/scl debug scl reg: /customer/riu_r 1210; /customer/riu_r 1211; /customer/riu_r 1212 /customer/riu_r 1213; /customer/riu_r 1214; /customer/riu_r 1215 /customer/riu_r 1218; /customer/riu_r 1219; /customer/riu_r 121a /customer/riu_r 1225; /customer/riu_r 122f cat /sys/class/mstar/mscl/ints echo vpescl 8 > /sys/class/mstar/mscl/dbgmg echo halif 6 > /sys/class/mstar/mscl/dbgmg echo irq 83 > /sys/class/mstar/mscl/dbgmg cat /proc/kmsg /customer/riu_r 1302 /customer/riu_r 1304 /customer/riu_r 1308 cat /sys/class/mstar/isp0/isp_info cat /sys/class/mstar/isp0/isp_ints

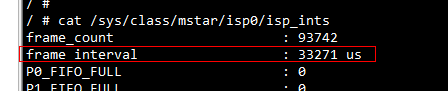

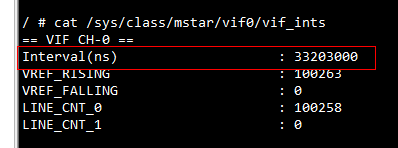

3.3. Vsync 不均匀¶

查看interval 时间是否均匀, 不均匀找对应owner 分析。 如果Vif这边不均匀还需要看下csi 信号接收是否有ERR_CNT

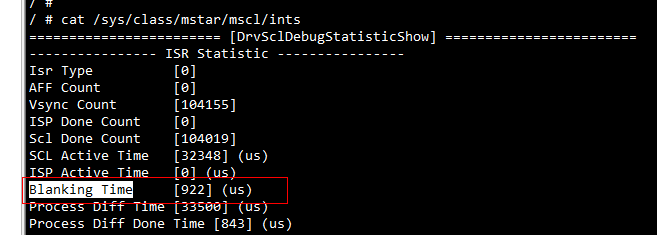

3.4. Blanking 太短¶

这里说的Blanking 是指Sc Done 到下一帧Vsync 的时间。

可以通过scl ints 看到对应时间, 一般应该要在500us 以上, 如果太短需要调整sensor 的vts 来调整, 调整关系为:

line_period = HMAX/(INCK*1000000) frame_interval = line_period * VMAX*1000

INCK: master clock, 通过sensor spec 和 reg 设定得到, 一般通过降低HMAX, 提高VMAX 提高Blanking。