SPI使用参考

1. 概述¶

1.1. SPI概述¶

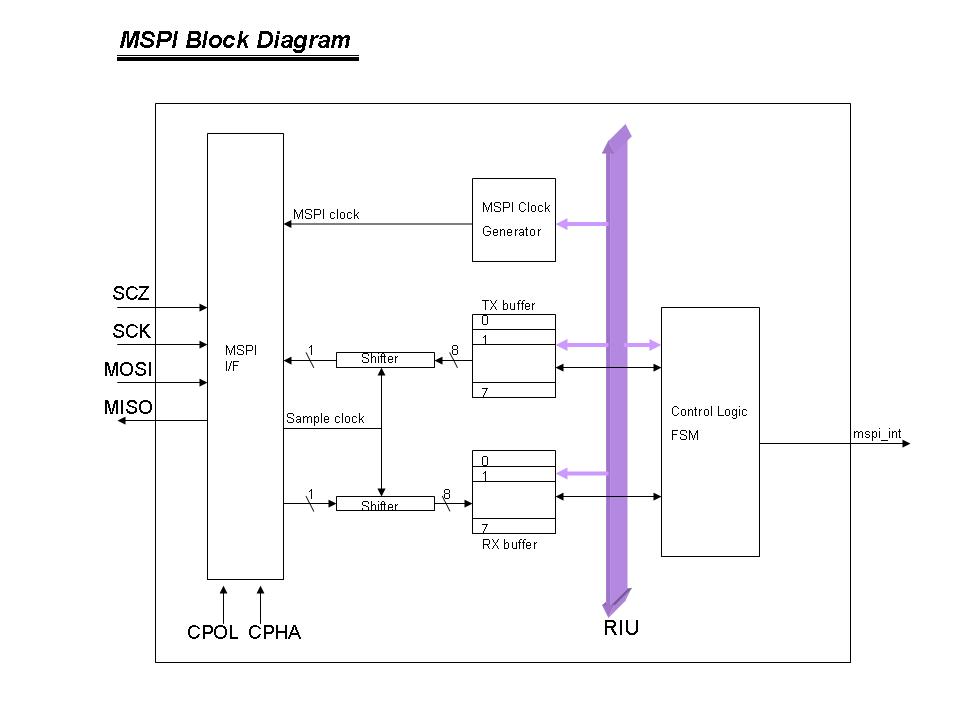

本文介绍了主SPI(MSPI)控制器。 MSPI是一个同步串行接口,可以连接各种外部设备。

1.2. MSPI特点¶

-

具有半双工的通用SPI协议。

-

支持Motorola SPI兼容时序。(CPHA / CPOL)

-

8字节读写缓冲区。

-

字节传输1位到8位可配置位宽度。

-

最多支持8个从设备选择信号。

-

支持3线模式。

-

支持内部RIU(寄存器接口单元)接口。 RIU是SigmaStar的内部协议。

1.3. MSPI框图¶

2. SPI控制¶

2.1. SPI控制概述¶

本节对启用MSPI前寄存器的初始化、MSPI的触发以及MSPI状态检查进行介绍。

2.2. 寄存器初始化¶

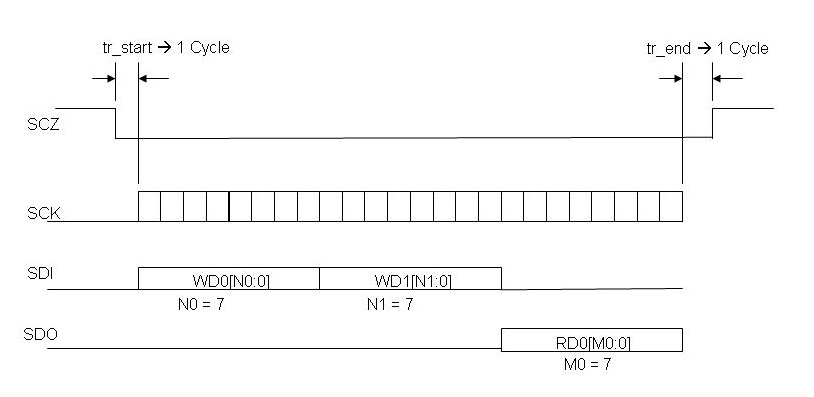

MSPI可配置参数如下图所示:

-

直流时序设置

“tr_start”: SCZ有效设置时间(相对于SCK)

“tr_end”: SCZ有效保持时间(相对于SCK)

“tb” : 帧传输之间的延迟周期

“trw”: 最后一次写入和第一次读取之间的延迟周期。 (读取回转周期)

-

写入/读取帧长度设置 (0x8830, 0x8831)

帧长:0~8 Bytes

-

每帧读/写位长度设置 (0x884c, 0x884e)

位长: 1~ 8 bit

-

时钟和相位控制 (0x8849)

Bit[7]: Clock Polarity, CPOL.

空闲状态下,SCK电平设置

0: 设为0时是低电平

1: 设为1时是高电平

Bit[6]: Clock Phase, CPHA

0: SCK启用时对日期进行采样。

1: SCK回到待机状态时对日期进行采样

-

重置并启用 (0x8849)

Bit[2]: 使能MSPI中断

0: 禁用

1: 启用

Bit[1]: 重置

0: 重置

1: 保持

Bit[0]: 启用MSPI

0: 禁用

1: 启用

-

启用芯片选择 (0x885f)

SPI Device1的芯片选择

0: 启用

1: 禁用

2.3. MSPI触发¶

MSPI触发 (0x885a, Bit[0])

-

bit设置为1时,MSPI控制器触发。

-

bit为write-clear寄存器

2.4. MSPI状态¶

MSPI完成标志 (0x885b, Bit[0])

-

MSPI操作完成后,在开始之前硬件将此位置高电平,到下一次数据传输时,SW需要通过(0x885c, Bit[0])清除该位。

-

当MSPI操作完成时,MSPI向CPU、SW发出中断通过(0x885c, Bit[0])清除中断。

2.5. MSPI读取数据端口¶

MSPI操作完成后,SW可以从以下读取端口获取数据

0x8844

0x8845

0x8846

0x8847

3. 示例说明¶

3.1. SPI操作示例¶

本节描述了MSPI操作的示例。

(0)初始化

(1)CS变低电平

(2)写入2 Bytes数据

(3)读取1 Bytes的数据

(4)CS变高电平

WREG[0x8849] = 0x07 //Enable MSPI, Not Reset, Enable INT //CPOL =0, CPHA=0 WREG[0x8849] = 0x00 //MSPI clock = CPU Clock/2 WREG[0x884a] = 0x00 //tr_start = 1 Cycle WREG[0x884a] = 0x00 //tr_end = 1 Cycle WREG[0x884b] = 0x00 //tb = 0 cycle WREG[0x884b] = 0x00 //trw = 0 Cycle WREG[0x8840] = DATA0 //Write buffer0 WREG[0x8841] = DATA1 //Write buffer1 WREG[0x8830] = 0x02 //Write length = 2 WREG[0x8830] = 0x01 //Read length = 1 WREG[0x884c], BIT[2:0] = 3’b111 //Bit length=8Bit for write buffer0 BIT[5:3] = 3’b111 //Bit length=8Bit for write buffer1 WREG[0x884e], BIT[2:0] = 3’b111 //Bit length=8Bit for read buffer0 WREG[0x8869], BIT[0] = 1’b0 //Select cs0 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x885b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt WREG[0x8869], BIT[0] = 1’b1 //Disable cs0

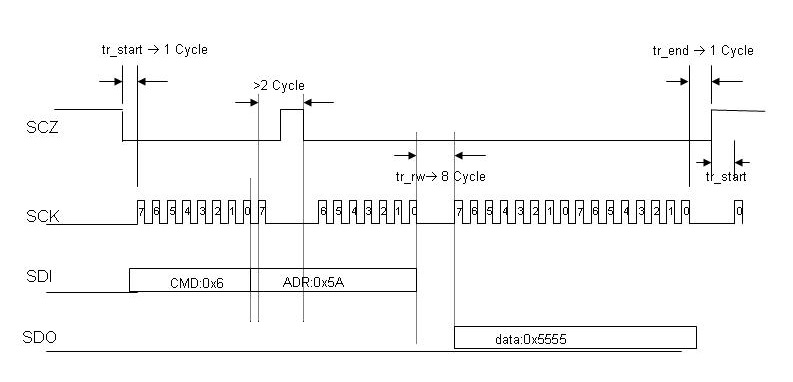

3.2. MSPI Connect to Incense 示例代码¶

-

Register Write to Incense: WREG[0x5a] = 16’h5555

WREG[0x8849] = 0x07 //Enable MSPI, Not Reset, Enable INT //CPOL =0, CPHA=0 WREG[0x8849] = 0x00 //MSPI clock = CPU Clock/2 WREG[0x884a] = 0x00 //tr_start = 1 Cycle WREG[0x884a] = 0x01 //tr_end = 2 Cycle WREG[0x884b] = 0x00 //tb = 0 cycle WREG[0x884b] = 0x00 //trw = 0 Cycle WREG[0x8840] = 0x03 (CMD) //Write buffer0 WREG[0x8841] = 0x5A (ADR) //Write buffer1 WREG[0x8830] = 0x02 //Write length = 2 WREG[0x884c], BIT[2:0] = 3’b111 //Bit length=8Bit for write buffer0 BIT[5:3] = 3’b000 //Bit length=1Bit for write buffer1 WREG[0x8869], BIT[0] = 1’b0 //Select cs0 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x885b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt WREG[0x8869], BIT[0] = 1’b1 //Disable cs0 ADR = ADR << 1; WREG[0x8840] = ADR //Write buffer0 WREG[0x8841] = 0x55(DATA0) //Write buffer1 WREG[0x8842] = 0x55(DATA1) //Write buffer2 WREG[0x8830] = 0x03 //Write length = 3 WREG[0x884c], BIT[2:0] = 3’b110 //Bit length=7Bit for write buffer0 BIT[5:3] = 3’b111 //Bit length=8Bit for write buffer1 BIT[8:6] = 3’b111 //Bit length=8Bit for write buffer2 WREG[0x8869], BIT[0] = 1’b0 //Select cs0 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x885b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt WREG[0x8869], BIT[0] = 1’b1 //Disable cs0

-

Register Read from Incense: RREG[0x5a]

WREG[0x8849] = 0x07 //Enable MSPI, Not Reset, Enable INT //CPOL =0, CPHA=0 WREG[0x8849] = 0x00 //MSPI clock = CPU Clock/2 WREG[0x884a] = 0x00 //tr_start = 1 Cycle WREG[0x884a] = 0x01 //tr_end = 2 Cycle WREG[0x884b] = 0x00 //tb = 0 cycle WREG[0x884b] = 0x00 //trw = 0 Cycle WREG[0x8840] = 0x06 (CMD) //Write buffer0 WREG[0x8841] = 0x5A (ADR) //Write buffer1 WREG[0x8830] = 0x02 //Write length = 2 WREG[0x884c], BIT[2:0] = 3’b111 //Bit length=8Bit for write buffer0 BIT[5:3] = 3’b000 //Bit length=1Bit for write buffer1 WREG[0x8869], BIT[0] = 1’b0 //Select cs0 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x885b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt WREG[0x8869], BIT[0] = 1’b1 //Disable cs0 ADR = ADR << 1; WREG[0x8840] = ADR //Write buffer0 WREG[0x8841] = 0x01 //Write length = 1 WREG[0x884c], BIT[2:0] = 3’b110 //Bit length=7Bit for write buffer0 WREG[0x8869], BIT[0] = 1’b0 //Select cs0 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x885b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt WREG[0x8849], BIT[7:6]= 2’b01 //CPOL =0, CPHA=1 //Change mode for read data WREG[0x884a] = 0x08 //tr_start = 8 Cycle //In this case trw = tr_start WREG[0x8830] = 0x00 //Write length = 0 WREG[0x8830] = 0x02 //Read length = 2 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x85b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt WREG[0x8869], BIT[0] = 1’b1 //Disable cs0 WREG[0x8830] = 0x01 //Read length = 1 //Dummy read WREG[0x884c, BIT[2:0] = 3’b000 //Bit length=1Bit for read buffer0 WREG[0x885a], BIT[0] = 1’b1 //Trigger MSPI operation Done = RREG[0x885b, Bit[0]] //Polling MSPI done flag Or interrupt WREG[0x885c], BIT[0] = 1’b1 //Clear done flag or clear interrupt