Pin脚复用

1. 概述¶

1.1. PadMux dtsi¶

Pad mux dtsi文件路径:kernel\arch\arm\boot\dts\infinity6e-padmux.dtsi。

如果是qfn封装chip,则路径为kernel\arch\arm\boot\dts\infinity6e-padmux-qfn.dtsi。

根据项目需求,修改该文件可设置pin 脚的复用模式。

第一列为pin脚名称,第二列pin脚复用模式,参考m_stPadMuxTbl 数组中的mode选项,第三列为复用功能中具体的pin脚作用,参考mdrv_puse.h。

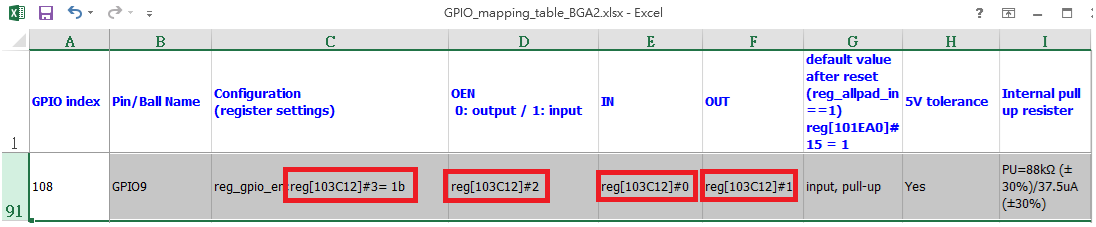

1.2. GPIO映射表¶

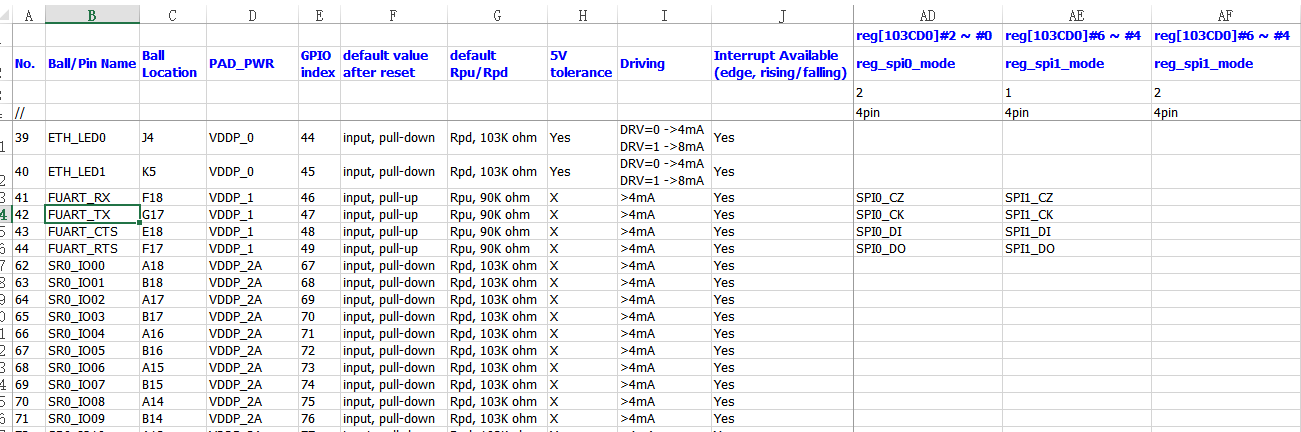

每一个chip都有一个gpio map文件,命名一般为SSCxxx GPIO_mapping_table.xlsx,下表显示每一个pin脚可复用的功能和对应的寄存器设置。

1.3. PadMux表¶

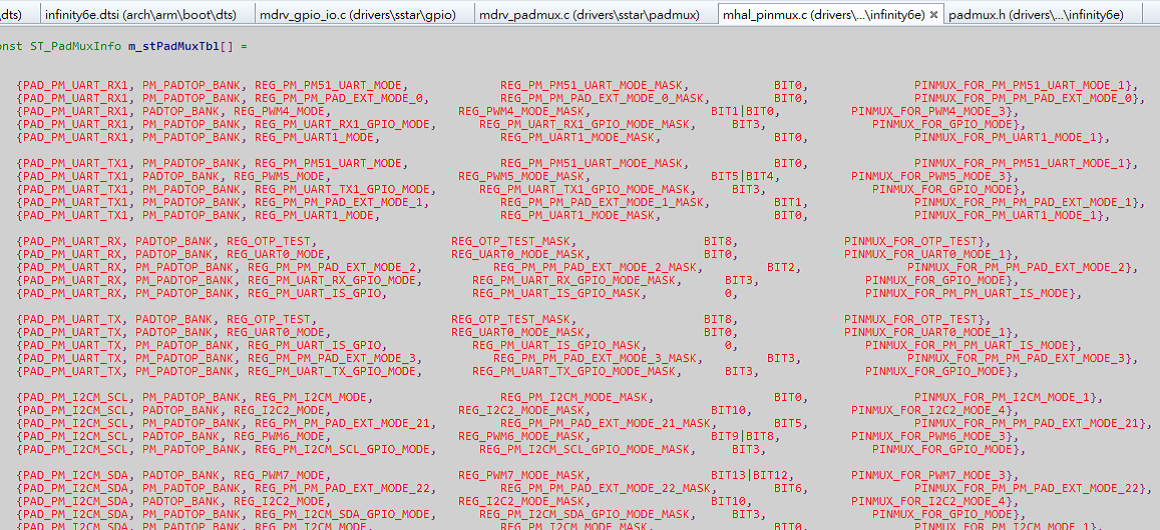

每个pin脚具体的复用功能也可见mhal_pinmux.c的m_stPadMuxTbl数组。复用关系优先级从高到低,GPIO功能的优先级最低。复用pin脚某个功能前要确认高优先级复用是关闭的。

PAD_FUART_TX: 引脚 CHIPTOP_BANK: 寄存器地址 REG_SR_PCK_MODE: 偏移地址 REG_PWM0_MODE_MASK mask位 BIT1|BIT0 对应的设置bit位 PINMUX_FOR_PWM0_MODE_3: 模式

2. PADMUX DTSI 设置示例¶

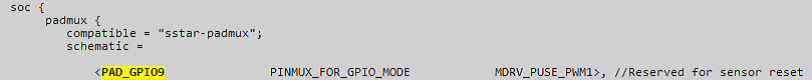

2.1. 设置PAD_GPIO9为 gpio模式¶

在pamux dtsi里面设置成对应的模式

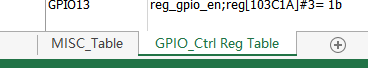

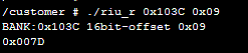

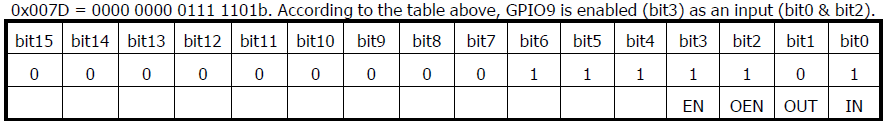

查看PAD_GPIO9 在mapping table表格中的设置,通过读寄存器来确认设置成功。

注意:当设置GPIO Mode的时候,请参考表格GPIO_Ctrl Reg Table sheet,其余模式参考MISC table sheet。

寄存器设置: reg[103C12]#0 / #1 / #2 / #3, 103C 为寄存器组, 偏移值是12。

必须将地址除以2才能将其转换为riu_r可读的格式:0x12 / 2 = 0x9(bit7〜bit0)

#./riu_r 0x103C 0x09

2.2. 设置 PAD_I2S0_xxx 为PWM 模式¶

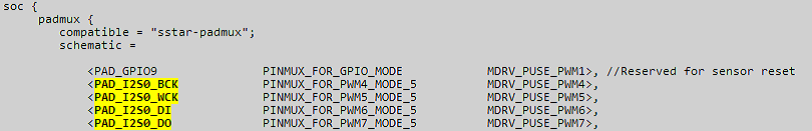

在 padmux dtsi里面设置成对应的模式

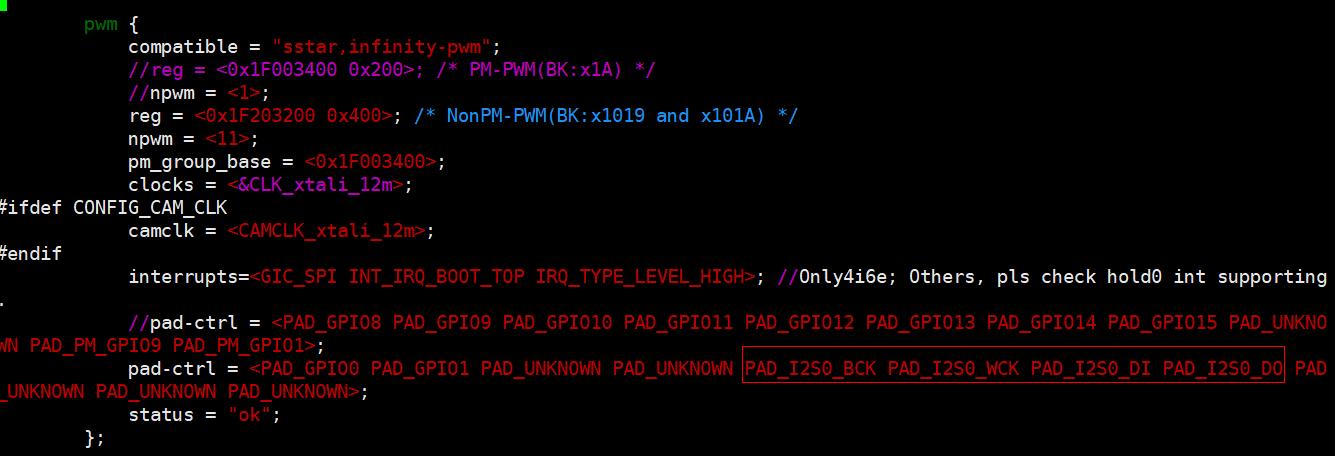

在 infinity6e.dtsi中设置设备树

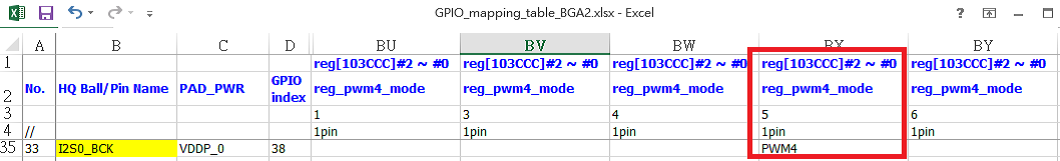

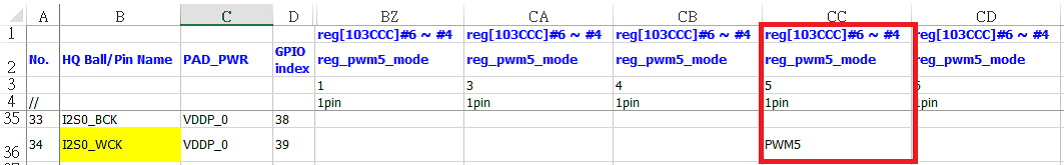

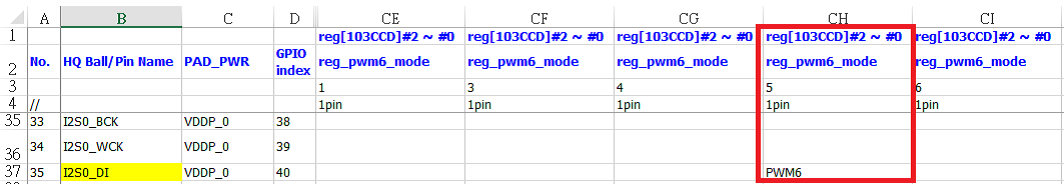

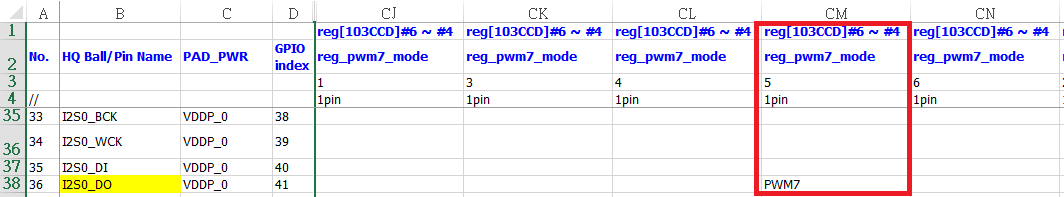

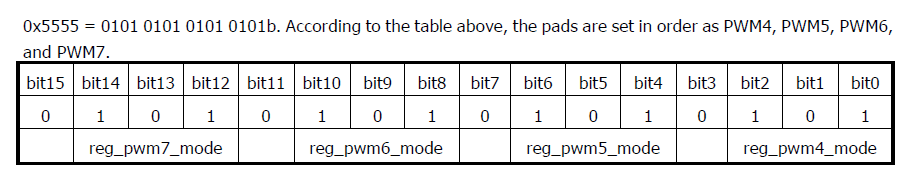

下图显示了PAD _I2S0 _xxx到GPIO映射表的映射:

寄存器设置: reg[103CCC]#2~#0 / #6~#4; reg[103CCD]#2~#0 / #6~#4;

103C 为寄存器组, 偏移值是 CC 。

必须将地址除以2才能将其转换为riu_r可读的格式:0xCC / 2 = 0x66(bit7〜bit0)

CD是偏移值。 必须将地址除以2才能将其转换为riu_r可读的格式:0xCD / 2 = 0x66(bit15〜bit8)./riu_r 0x103C 0x66

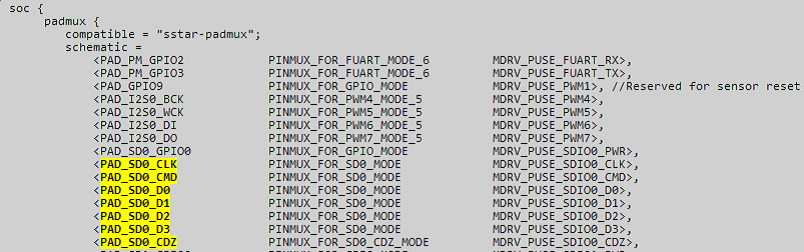

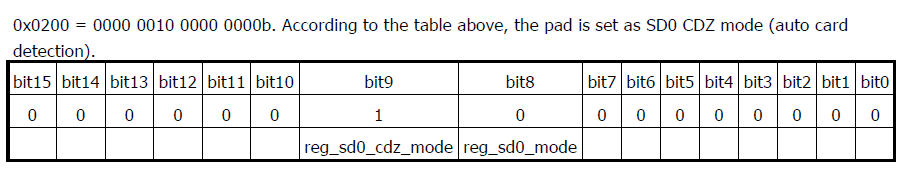

2.3. .设置PAD_SD0_xxx 为 SD0模式¶

在 padmux dtsi里面设置成对应的模式

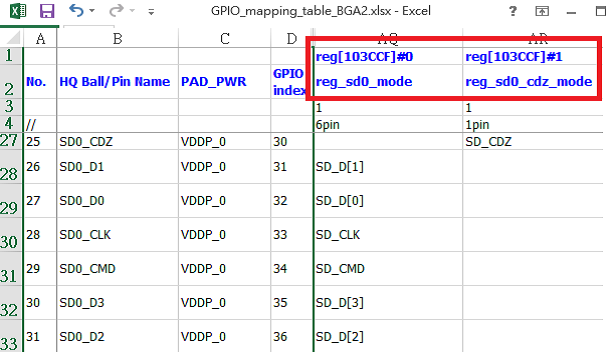

下图显示了PAD_SD0_xxx到GPIO映射表的映射:

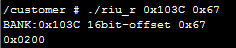

Register 设定: reg[103CCF]#0 / #1, 103C 是寄存器组,CF是偏移值。

必须将地址除以2才能将其转换为riu_r可读的格式:0xCF / 2 = 0x67(bit15〜bit8)./riu_r 0x103C 0x67

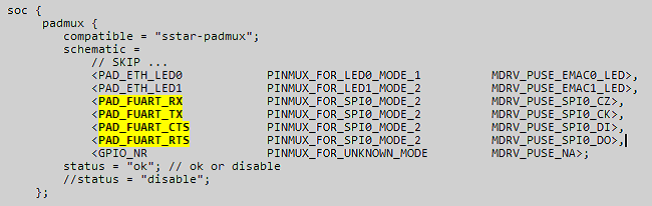

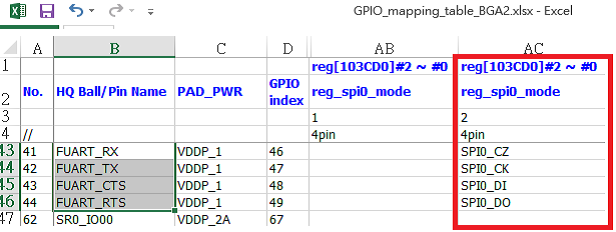

2.4. 设置PAD_FUART_xxx 为 SPI 模式¶

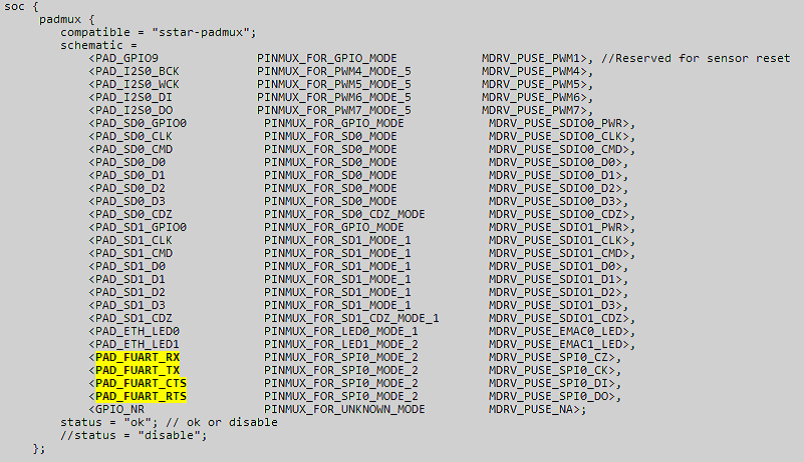

在 padmux dtsi里面设置成对应的模式

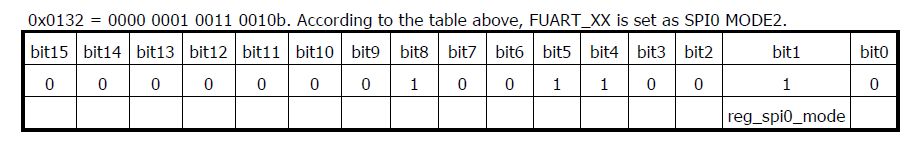

下图显示了PAD _FUART _xxx到GPIO映射表的映射:

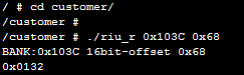

寄存器设置:reg[103CD0]#2~#0, 103C 是寄存器组,D0是偏移值,必须将地址除以2才能将其转换为riu _r 可读的格式:0xD0 / 2 = 0x68(bit7 \〜bit0)

#./riu_r 0x103C 0x68